## HIGH-SPEED MICROCONTROLLER USER'S GUIDE: NETWORK MICROCONTROLLER SUPPLEMENT

This document is provided as a supplement to the *High-Speed Microcontroller User's Guide*, covering new or modified features specific to the DS80C400/DS80C410/DS80C411. **This document must be used in conjunction with the High-Speed** *Microcontroller User's Guide, available from Maxim.* Addenda are arranged by section number, which correspond to sections in the *High-Speed Microcontroller User's Guide*.

Unless otherwise specified, the references to the DS80C400 and its features also apply to the DS80C410 and DS80C411. Exceptions include differences in the amount of internal memory and the inclusion/exclusion of the CAN module.

The following additions and changes, with respect to the High-Speed Microcontroller User's Guide, are contained in this document. This document is a work in progress, and updates/additions are added when available.

| TABLE OF CONTENTS<br>ADDENDUM TO SECTION 1: INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

| ADDENDUM TO SECTION 2: ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                |

| Refer to the device-specific data sheet(s) for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . –                                                                                                                               |

| ADDENDUM TO SECTION 3: ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                                                                                |

| CPU Core and CPU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .15                                                                                                                               |

| ADDENDUM TO SECTION 4: PROGRAMMING MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                                                |

| Memory Map         Register Map         Bit-Addressable Locations         Working Registers         Stack         Special-Function Register Maps         Special-Function Register Map         Special-Function Register Map         Special-Function Register Map         Special-Function Register Location         Special-Function Register Reset Values         Special-Function Registers         Port 4 (P4)         Stack Pointer (SP)         Data Pointer Low 0 (DPL)         Data Pointer Low 1 (DPL1)         Data Pointer Low 1 (DPH1)         Data Pointer Low 1 (DPH1)         Data Pointer Select (DPS)         Power Control (PCON)         Timer/Counter Control (TCON)         Timer 0 LSB (TL0)         Timer 1 LSB (TL1)         Timer 0 LSB (TL0)         Timer 1 MSB (TH1)         Clock Control (CKCON)         Port 1 (P1)         External Interrupt Flag (EXIF)         Port 4 Control Register (P4CNT)         Data Pointer Extended Register 0 (DPX) | .16<br>.17<br>.17<br>.17<br>.17<br>.17<br>.17<br>.18<br>.21<br>.25<br>.25<br>.25<br>.25<br>.25<br>.25<br>.25<br>.25<br>.25<br>.25 |

| Data Pointer Extended Register 1 (DPX1)                            |     |

|--------------------------------------------------------------------|-----|

| CAN 0 Receive Message Stored Register 0 (C0RMS0)                   | .36 |

| CAN 0 Receive Message Stored Register 1 (C0RMS1)                   |     |

| Serial Port 0 Control (SCON0)                                      |     |

| Serial Data Buffer 0 (SBUF0) Extended Stack Pointer Register (ESP) |     |

| Address Page Register (AP)                                         |     |

| Address Control Register (ACON)                                    |     |

| CAN 0 Transmit Message Acknowledgment Register 0 (C0TMA0)          |     |

| CAN 0 Transmit Message Acknowledgment Register 1 (C0TMA1)          |     |

| Port 2 (P2)                                                        |     |

| Port 5 (P5)                                                        |     |

| Port 5 Control Register (P5CNT)                                    | .44 |

| CAN 0 Control Register (C0C)                                       |     |

| CAN 0 Status Register (C0S)                                        |     |

| CAN 0 Interrupt Register (C0IR)                                    |     |

| CAN 0 Receive-Error Register (CORE)                                |     |

| Interrupt Enable (IE)                                              |     |

| Slave Address Register 0 (SADDR0)                                  |     |

| Slave Address Register 1 (SADDR1)                                  |     |

| CAN 0 Message Center 1 Control Register (C0M1C)                    | .56 |

| CAN 0 Message Center 2 Control Register (C0M2C)                    | .59 |

| CAN 0 Message Center 3 Control Register (COMSC)                    |     |

| CAN 0 Message Center 4 Control Register (COM4C)                    |     |

| Port 3 (P3)                                                        |     |

| Port 6 (P6)                                                        |     |

| Port 6 Control Register (P6CNT)                                    |     |

| CAN 0 Message Center 6 Control Register (C0M6C)                    |     |

| CAN 0 Message Center 7 Control Register (C0M7C)                    |     |

| CAN 0 Message Center 8 Control Register (C0M8C)                    |     |

| CAN 0 Message Center 9 Control Register (C0M9C)                    | .64 |

| CAN 0 Message Center 10 Control Register (C0M10C)                  | .64 |

| Interrupt Priority (IP)                                            | .65 |

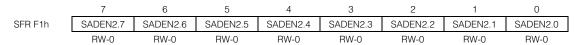

| Slave Address Mask Enable Register 0 (SADEN0)                      |     |

| Slave Address Mask Enable Register 1 (SADEN1)                      |     |

| CAN 0 Message Center 11 Control Register (C0M11C)                  |     |

| CAN 0 Message Center 12 Control Register (C0M12C)                  |     |

| CAN 0 Message Center 13 Control Register (C0M13C)                  |     |

| CAN 0 Message Center 14 Control Register (C0M14C)                  | .67 |

| CAN 0 Message Center 15 Control Register (C0M15C) | .67 |

|---------------------------------------------------|-----|

| Serial Port Control (SCON1)                       |     |

| Serial Data Buffer 1 (SBUF1)                      |     |

| Power-Management Register (PMR)                   |     |

| Status Register (STATUS)                          |     |

| Memory Control Register (MCON)                    |     |

| Timed-Access Register (TA)                        | 71  |

| Timer 2 Control (T2CON)                           | 72  |

| Timer 2 Mode (T2MOD)                              | 73  |

| Timer 2 Capture LSB (RCAP2L)                      |     |

| Timer 2 Capture MSB (RCAP2H)                      | 73  |

| Timer 2 LSB (TL2)                                 | 74  |

| Timer 2 MSB (TH2)                                 |     |

| Clock Output Register (COR)                       | 74  |

| Program Status Word (PSW)                         | 75  |

| Multiplier Control Register 0 (MCNT0)             | 76  |

| Multiplier Control Register 1 (MCNT1)             | 77  |

| Multiplier A Register (MA)                        | 77  |

| Multiplier B Register (MB)                        | 78  |

| Multiplier C Register (MC)                        | .79 |

| Memory Control Register 1 (MCON1)                 | .79 |

| Memory Control Register 2 (MCON2)                 | 81  |

| Watchdog Control (WDCON)                          | .82 |

| Slave Address Register 2 (SADDR2)                 | .83 |

| Breakpoint Address Register 1 (BPA1)              | 83  |

| Breakpoint Address Register 2 (BPA2)              | .83 |

| Breakpoint Address Register 3 (BPA3)              | .83 |

| Accumulator (AC)                                  | 84  |

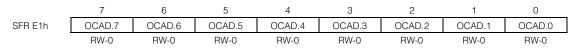

| One's Complement Adder Data (OCAD)                | 84  |

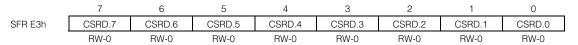

| CSR Data (CSRD)                                   | .84 |

| CSR Address (CSRA)                                | .84 |

| Ethernet Buffer Size (EBS)                        | .85 |

| Buffer Control Unit Data (BCUD)                   | .85 |

| Buffer Control Unit Control (BCUC)                | .86 |

| Extended Interrupt Enable (EIE)                   |     |

| MOVX Address Extended Register (MXAX)             |     |

| Data Pointer Extended Register 2 (DPX2)           | .88 |

| Data Pointer Extended Register 3 (DPX3)           | .88 |

| 1-Wire Master Address Register (OWMAD)            | .88 |

| 1-Wire Master Data Register (OWMDR)               | .89 |

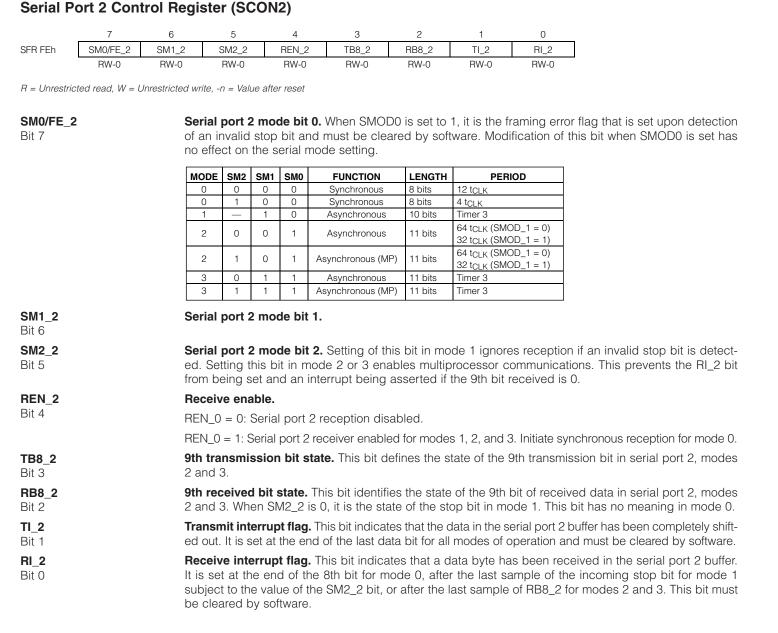

|   | B Register (B) .<br>Slave Address Mask Enable Register 2 (SADEN2) .<br>Data Pointer Low Register 2 (DPL2) .<br>Data Pointer High Register 2 (DPH2) .<br>Data Pointer Low Register 3 (DPL3) .<br>Data Pointer High Register 3 (DPH3) .<br>Data Pointer Select Register 1 (DPS1) .<br>Status Register 1 (STATUS1) .<br>Extended Interrupt Priority (EIP) .<br>Parallel I/O Port (P7) .<br>Timer 3 LSB (TL3) .<br>Timer 3 MSB (TH3) .<br>Timer 3 Control/Mode Register (T3CM) .<br>Serial Port 2 Control Register (SCON2) .<br>Serial Data Buffer 2 (SBUF2) . | .89<br>.90<br>.90<br>.90<br>.90<br>.91<br>.91<br>.92<br>.92<br>.92<br>.93<br>.94 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

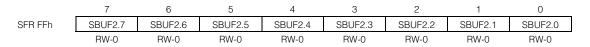

|   | DDENDUM TO SECTION 5: CPU TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                                                                               |

|   | External Clock SourceSystem Clock SelectionChanging the System Clock/Machine Cycle Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .95<br>.96                                                                       |

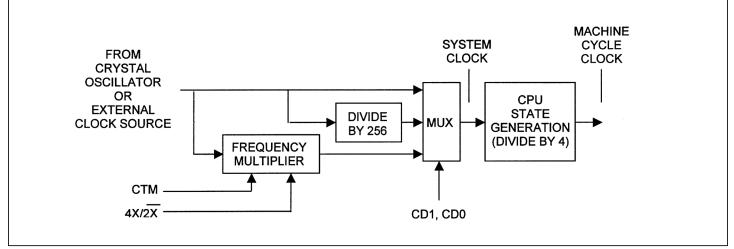

|   | DDENDUM TO SECTION 6: MEMORY ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                               |

|   | Internal Program Memory<br>Internal Data Memory<br>DS80C400<br>DS80C410/DS80C411<br>External Memory Access<br>Using the Combined Chip-Enable Signals<br>Write-Protection Feature (DS80C400 Only)<br>Enhanced Quad Data Pointers                                                                                                                                                                                                                                                                                                                            | .98<br>.98<br>.99<br>.100<br>.104<br>.108                                        |

| A | DDENDUM TO SECTION 7: POWER MANAGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109                                                                              |

|   | Precision Voltage Monitor<br>Early Warning Power-Fail Interrupt<br>Power-Fail Reset<br>Power-On Reset<br>Bandgap Select<br>Power-Management Summary<br>Power-Management Modes<br>PMM and Peripheral Functions<br>Switchback                                                                                                                                                                                                                                                                                                                                | .110<br>.110<br>.110<br>.110<br>.110<br>.110<br>.110                             |

| Stop Mode                                         |      |

|---------------------------------------------------|------|

| Pin States in Idle or Stop Mode                   |      |

| Switching Between Clock Sources                   |      |

|                                                   | 111  |

| Reset Sources                                     |      |

| Power-On/Power-Fail Reset                         |      |

|                                                   |      |

| Oscillator Fail-Detect Reset                      |      |

| Reset Outputs                                     | .113 |

| Reset Output Low (RSTOL)                          |      |

| Reset State                                       |      |

| ADDENDUM TO SECTION 9: INTERRUPTS                 | 114  |

|                                                   |      |

| ADDENDUM TO SECTION 10: PARALLEL I/O              | 116  |

| Port 0                                            |      |

| Ports 4–7                                         |      |

| General-Purpose I/O                               |      |

| Current-Limited Transitions                       |      |

| 5V-Tolerant I/O                                   |      |

| ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS       | 118  |

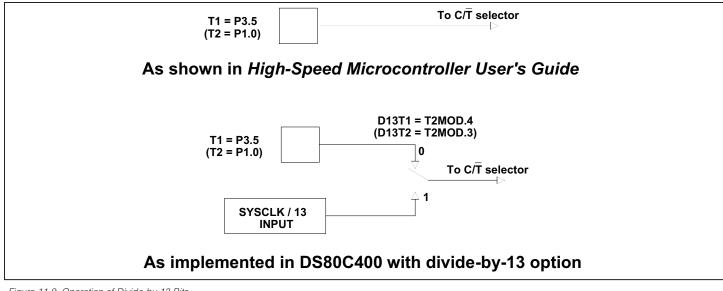

| Divide-by-13 Option                               | .122 |

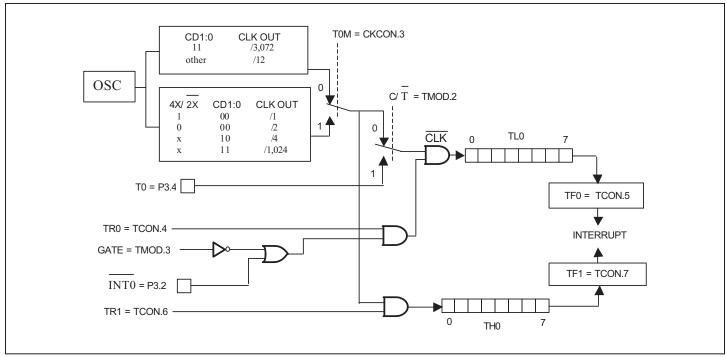

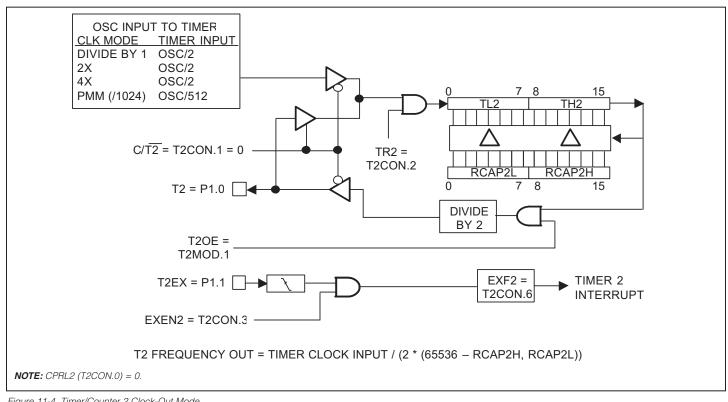

| Programmable Clock Output                         | .123 |

|                                                   |      |

| ADDENDUM TO SECTION 12: SERIAL I/O                | 124  |

| Serial Mode Summary                               |      |

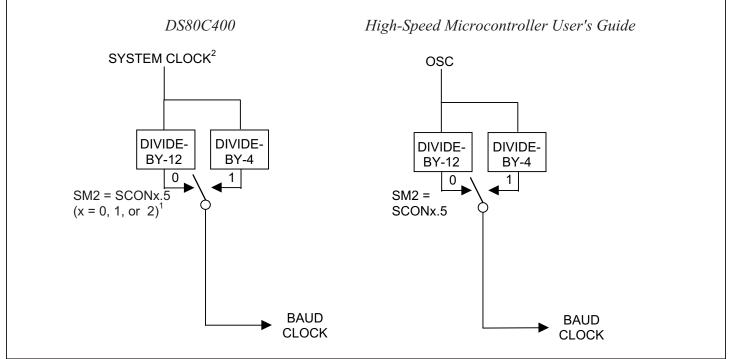

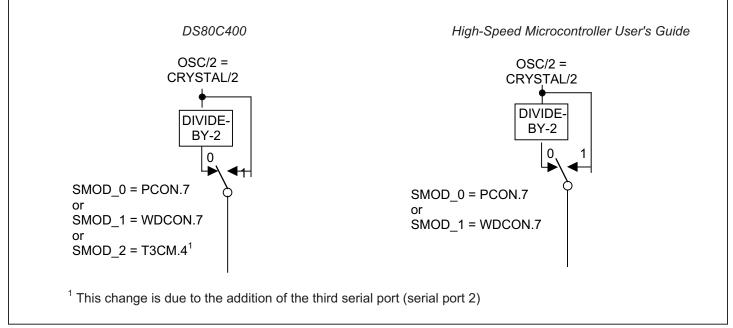

| Baud Rates                                        |      |

| Mode 0                                            |      |

| Mode 1 or 3                                       |      |

| Using Timer 1 or Timer 3 for Baud-Rate Generation |      |

| Using Timer 2 for Baud-Rate Generation            |      |

| ADDENDUM TO SECTION 13: TIMED-ACCESS PROTECTION   | 129  |

| ADDENDUM TO SECTION 14: REAL-TIME CLOCK           | 129  |

Refer to the High-Speed Microcontroller User's Guide. Not applicable to the DS80C400/410/411.

| ADDENDUM TO SECTION 15: BATTERY BACKUP                                                                                                                                                                                                                                                                                          | 129       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Refer to the High-Speed Microcontroller User's Guide. Not applicable to the DS80C400/                                                                                                                                                                                                                                           | '410/411. |

| ADDENDUM TO SECTION 16: INSTRUCTION SET DETAILS                                                                                                                                                                                                                                                                                 | 130       |

| 16-Bit (8051 Standard) Addressing Mode                                                                                                                                                                                                                                                                                          |           |

| ADDENDUM TO SECTION 17: TROUBLESHOOTING                                                                                                                                                                                                                                                                                         | 133       |

| Software Breakpoint Mode                                                                                                                                                                                                                                                                                                        | 133       |

| ADDENDUM TO SECTION 18: MICROCONTROLLER                                                                                                                                                                                                                                                                                         |           |

| DEVELOPMENT SUPPORT                                                                                                                                                                                                                                                                                                             | 135       |

| Refer to the High-Speed Microcontroller User's Guide.                                                                                                                                                                                                                                                                           |           |

| SECTION 19: CONTROLLER AREA NETWORK (CAN) MODULE                                                                                                                                                                                                                                                                                | 136       |

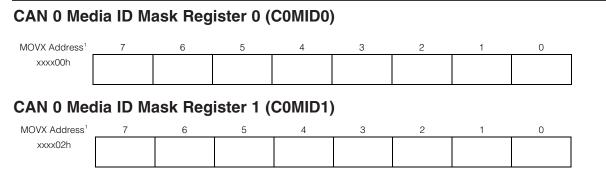

| MOVX Message Centers for CAN 0<br>CAN MOVX Register Description<br>CAN 0 Media ID Mask Register 0 (COMID0)<br>CAN 0 Media ID Mask Register 1 (COMID1)<br>CAN 0 Media Arbitration Register 0 (COMA0)<br>CAN 0 Media Arbitration Register 1 (COMA1)<br>CAN 0 Bus Timing Register 0 (C0BT0)<br>CAN 0 Bus Timing Register 1 (C0BT1) |           |

CAN 0 Standard Global Mask Register 0 (C0SGM0).142CAN 0 Standard Global Mask Register 1 (C0SGM1).142CAN 0 Extended Global Mask Register 0 (C0EGM0).142CAN 0 Extended Global Mask Register 1 (C0EGM1).142CAN 0 Extended Global Mask Register 2 (C0EGM2).142CAN 0 Extended Global Mask Register 3 (C0EGM3).143CAN 0 Message Center 15 Mask Register 0 (C0M15M0).143CAN 0 Message Center 15 Mask Register 2 (C0M15M1).143CAN 0 Message Center 15 Mask Register 3 (C0M15M1).143CAN 0 Message Center 15 Mask Register 3 (C0M15M3).144CAN 0 Message Center y Arbitration Register 0 (C0MyAR0).144CAN 0 Message Center y Arbitration Register 1 (C0MyAR1).144CAN 0 Message Center y Arbitration Register 3 (C0M15M2).144CAN 0 Message Center y Arbitration Register 3 (C0MyAR3).144

| CAN 0 Message Center y Format Register (C0MyF)       | 146 |

|------------------------------------------------------|-----|

| CAN 0 Message Center y Data Byte 0 (C0MyD0)          |     |

| CAN 0 Message Center y Data Byte 1 (C0MyD1)          |     |

| CAN 0 Message Center y Data Byte 2 (C0MyD2)          | 147 |

| CAN 0 Message Center y Data Byte 3 (C0MyD3)          |     |

| CAN 0 Message Center y Data Byte 4 (C0MyD4)          | 147 |

| CAN 0 Message Center y Data Byte 5 (C0MyD5)          | 147 |

| CAN 0 Message Center y Data Byte 6 (C0MyD6)          | 147 |

| CAN 0 Message Center y Data Byte 7 (C0MyD7)          | 147 |

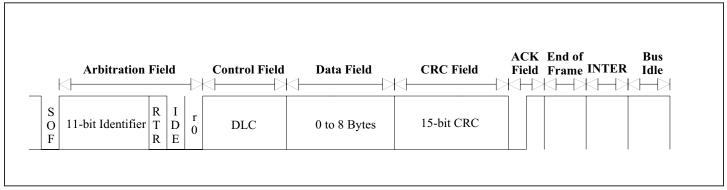

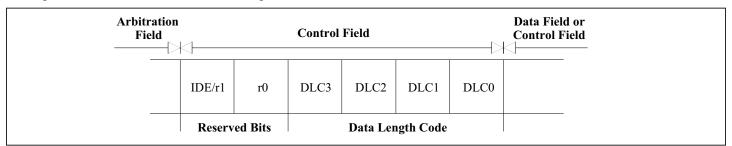

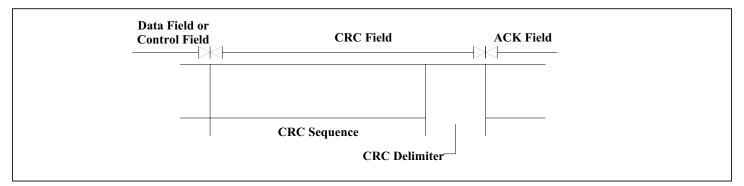

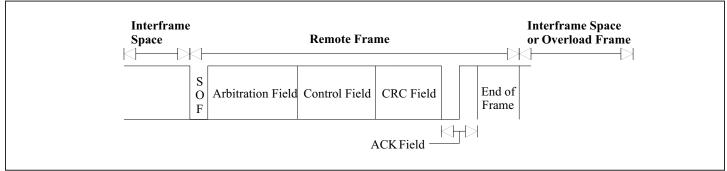

| Frame Types                                          | 148 |

| Initializing the CAN Controller                      | 152 |

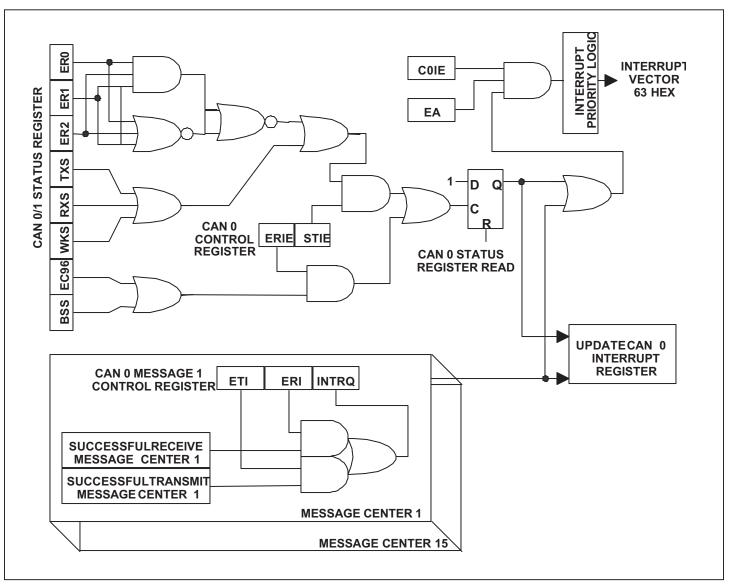

| CAN Interrupts                                       | 152 |

| Arbitration/Masking Considerations                   | 153 |

| Message Center 15                                    | 154 |

| Transmitting and Receiving Messages                  | 154 |

| Transmitting Data Messages                           |     |

| Receiving Data Messages                              |     |

| Transmitting Remote Frame Requests                   |     |

| Receiving/Responding to Remote Frame Requests        |     |

| Remote Frame Handling in Relation to the DTBYC Bits  |     |

| Overwrite Enable/Disable Feature                     |     |

| Case 1: WTOE = 1 (Overwrites allowed)                |     |

| Case 2: WTOE = 0 (Overwrites disabled)               |     |

| Special Considerations for Message Center 15         |     |

| Using the Autobaud Feature                           | 159 |

| Bus-Off/Bus-Off Recovery and Error Counter Operation |     |

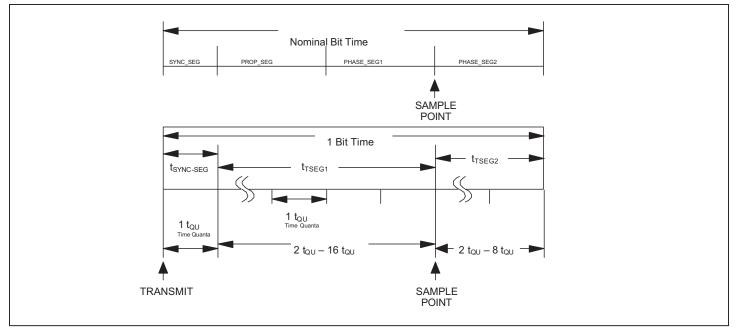

| Bit Timing                                           |     |

| Threefold Bit Sampling                               |     |

| Bus Rate Timing Example                              |     |

| Additional Bit Timing Examples                       | 164 |

| SECTION 20: ARITHMETIC ACCELERATOR                   | 165 |

| Divide (32-bit by 16-bit or 16-bit by 16-bit)        | 166 |

| Multiply (16-bit by 16-bit)                          |     |

| Shift right/left                                     |     |

| Normalize                                            | 167 |

| 40-Bit Accumulator                                   | 167 |

| SECTION 21: 1-WIRE BUS MASTER                        | 168 |

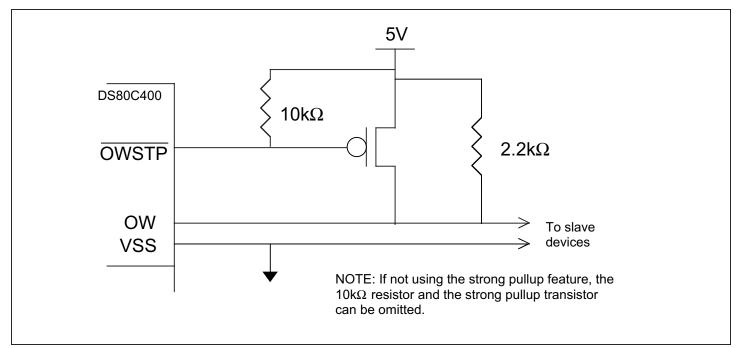

| Hardware Setup                                       |     |

|                                                      |     |

|    | Setting Up and Using the 1-Wire Master<br>Setting Up the 1-Wire Master<br>Sending a 1-Wire Reset<br>Sending a Byte<br>Search ROM Accelerator<br>Accelerated ROM Search Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .169<br>.169<br>.169<br>.170<br>.171                                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

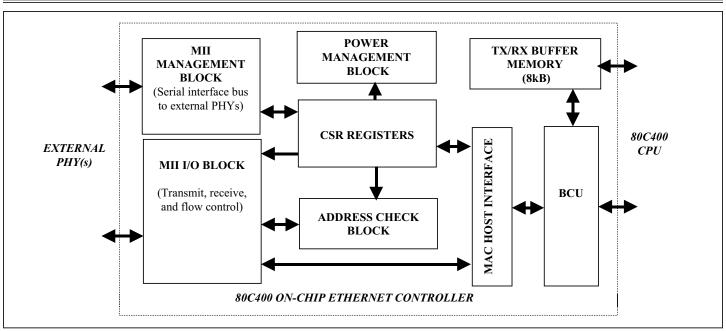

| S  | ECTION 22: ETHERNET CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 172                                                                                                  |

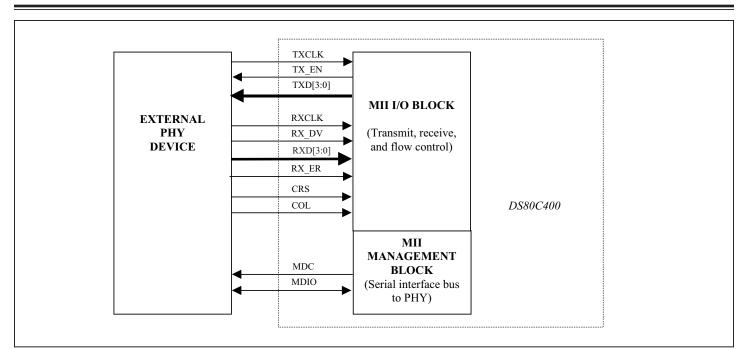

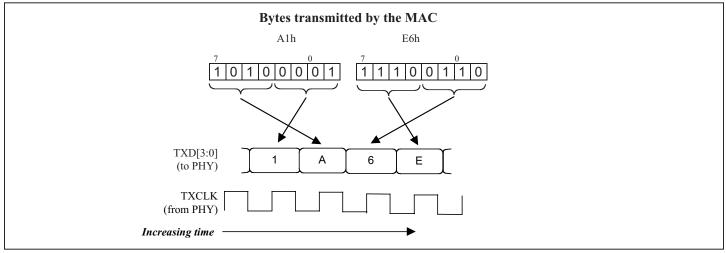

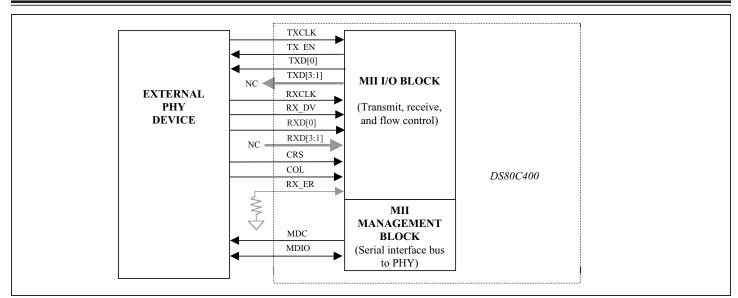

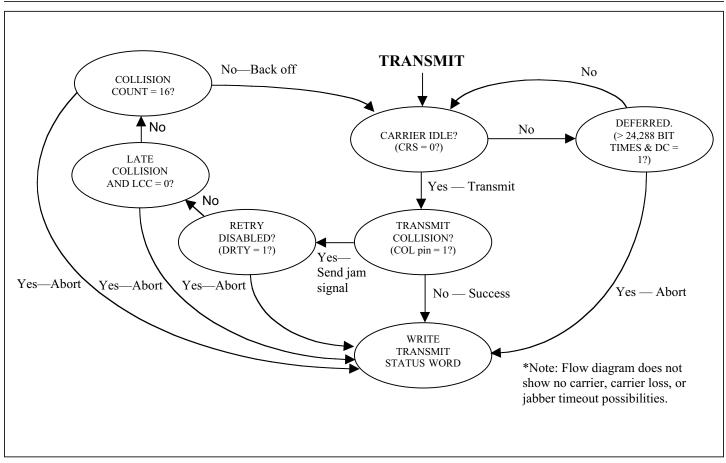

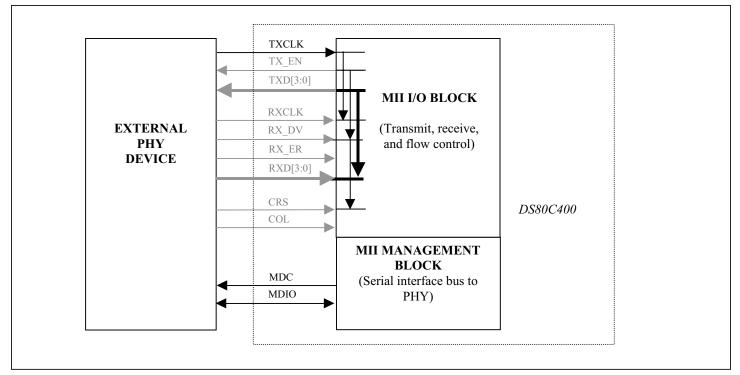

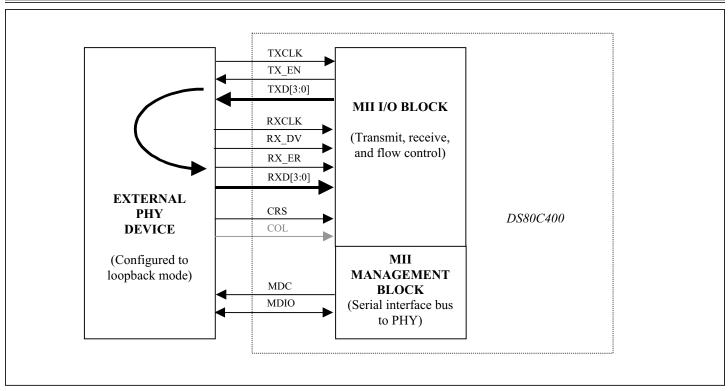

|    | Assigning a Physical MAC Address<br>Configuring the MAC Operational Mode<br>Media Independent Interface (MII)<br>ENDEC Operation<br>ENDEC Mode—Heartbeat Signal Quality Generator<br>MAC Primary Functions—Packet Filtering<br>Using the MII Serial Management Bus<br>Half-Duplex Operation—CSMA/CD and Flow Control<br>Deferral Check<br>Disable Retry<br>Back-Off Limit<br>Late Collision Control<br>Flow Control<br>Flow Control<br>Flow Control<br>Pause Control Frame<br>Loopback Modes<br>Address Filtering Control<br>Using the Hash Table<br>VLAN Support<br>Partitioning the 8kB Ethernet Data Buffer Memory<br>Transmit/Receive Data Buffer Word Orientation: Edianess<br>Transmiting Data<br>Receiving Data<br>Using Wake-Up Frames<br>Magic Packet Mode<br>Network Wake-Up Frame | .173<br>.174<br>.175<br>.176<br>.176<br>.177<br>.177<br>.177<br>.178<br>.178<br>.178<br>.178<br>.178 |

| SI | ECTION 23: EMBEDDED DS80C400 SILICON SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 189                                                                                                  |

|    | Serial Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      |

|    | Autobaud-Rate Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |

|    | Command Line Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |

|    | Command Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .189                                                                                                 |

| Exported RAM Functions                              | )  |

|-----------------------------------------------------|----|

| Utility Functions                                   | 1  |

| Memory Manager Functions                            | 3  |

| Socket Function Calling Conventions                 | 5  |

| Input Parameter Buffer                              | 5  |

| Output Return Values                                | 5  |

| Socket Functions/Pointers                           | 3  |

| PARAMBUFFER                                         | 3  |

| DHCP Functions                                      | 3  |

| TFTP Functions/Pointers                             | 1  |

| Task Scheduler Functions                            | 5  |

| Task Scheduler User Hooks                           | 3  |

| 1-Wire Master                                       | )  |

| Additional Functions Available in ROM Version 1.2.0 | )  |

| Initialization Functions                            | 1  |

| Asynchronous TCP/IP Maintenance Functions           | 3  |

| ROM Redirect Function Table                         | 7  |

| ROM Redirect Functions                              | 3  |

| Timeslice and Task Scheduler Timing                 | )  |

| REVISION HISTORY 22                                 | :1 |

# **LIST OF FIGURES**

| Figure 5-1. System Clock Control Diagram                                              | 95  |

|---------------------------------------------------------------------------------------|-----|

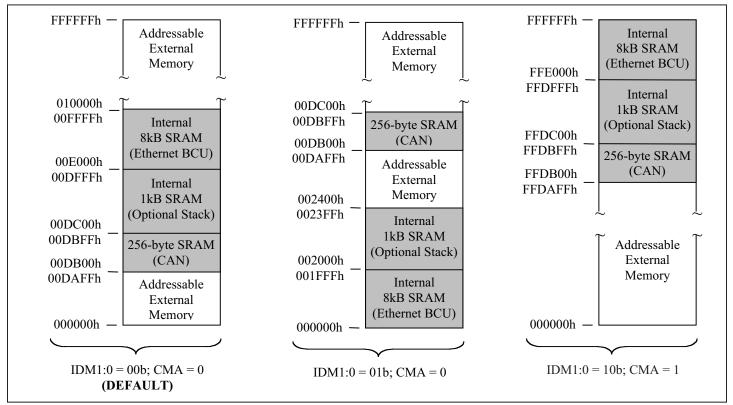

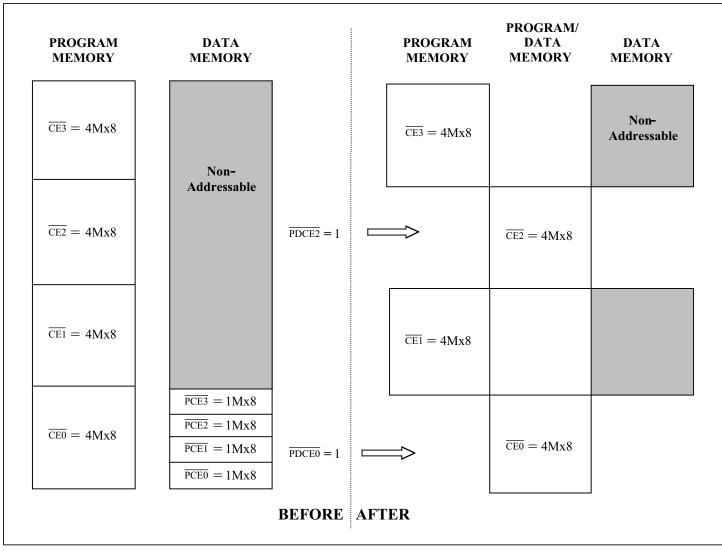

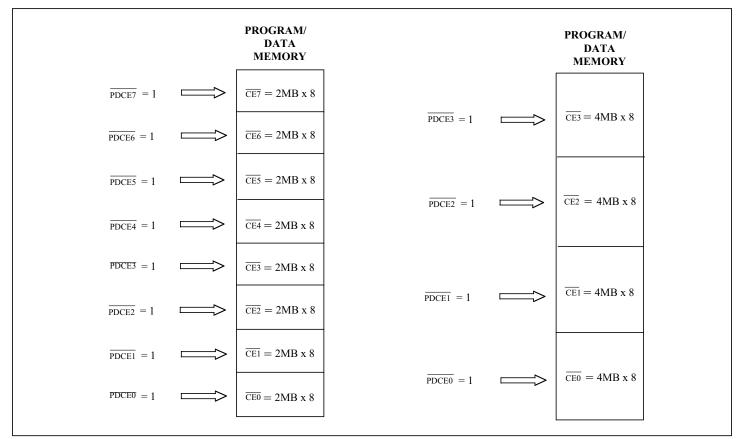

| Figure 6-1. Program Memory Map Options                                                | 97  |

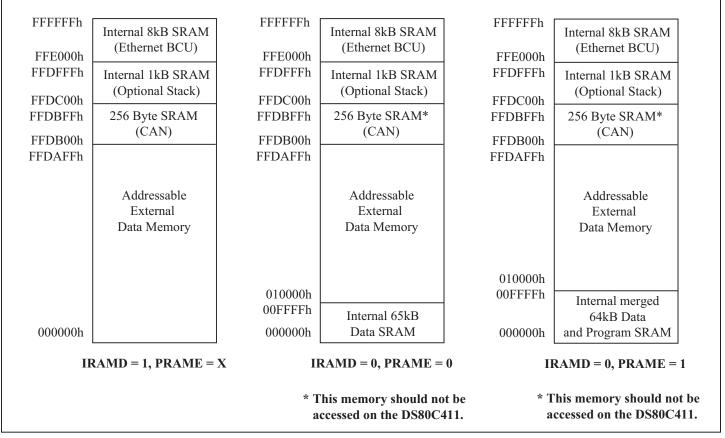

| Figure 6-2. Example Data Memory Map Configurations (DS80C400)                         | 98  |

| Figure 6-3. Example Data Memory Map Configurations (DS80C400/DS80C411)                | 99  |

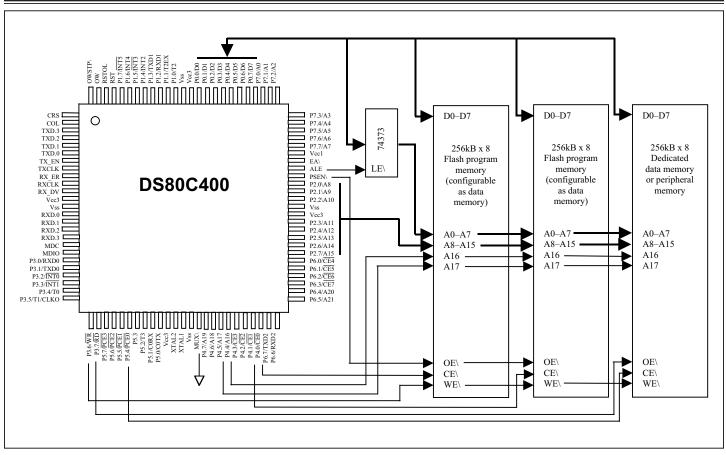

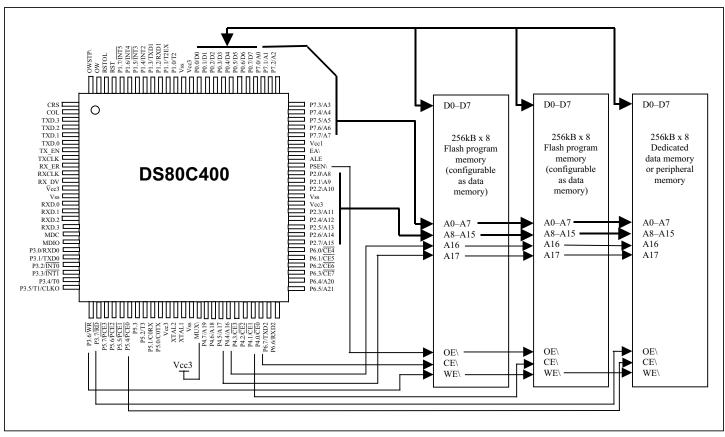

| Figure 6-4. Multiplexed Address/Data Bus                                              | 103 |

| Figure 6-5. Demultiplexed Address/Data Bus                                            | 104 |

| Figure 6-6. Merged Program/Data Access Under CE0, CE2, PCE0–PCE3                      |     |

| Becomes Inaccessible                                                                  | 105 |

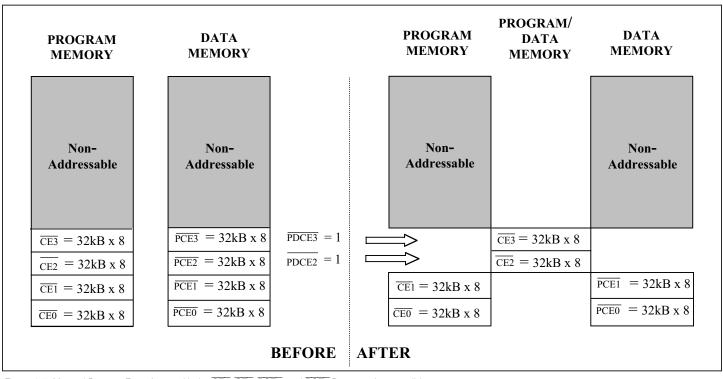

| Figure 6-7. Merged Program/Data Access Under CE2, CE3, PCE2, and PCE3                 |     |

| Becomes Inaccessible                                                                  | 106 |

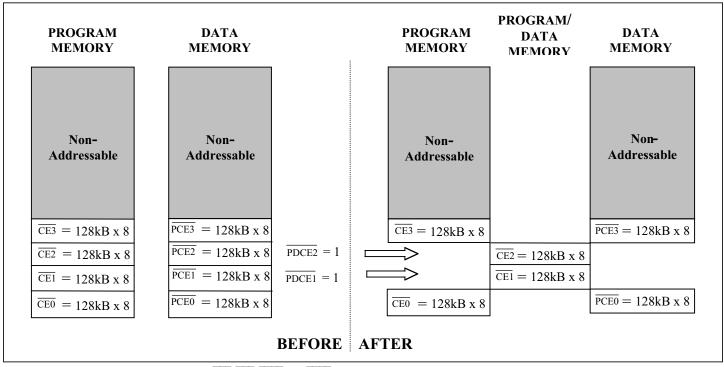

| Figure 6-8. Merged Program/Data Access Under CE1, CE2, PCE1, and PCE2                 |     |

| Becomes Inaccessible                                                                  | 106 |

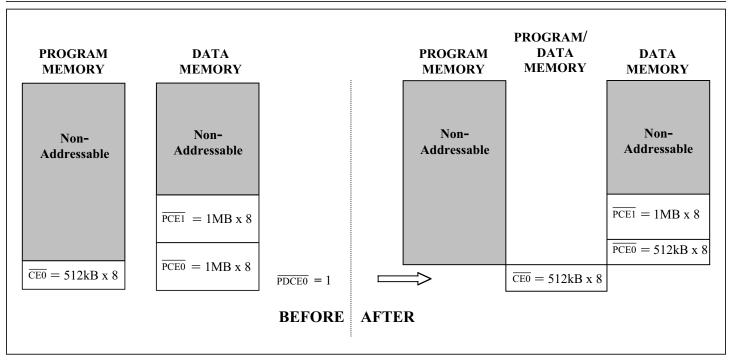

| Figure 6-9. Merged Program/Data Access Under CE0 and PCE0 Becomes                     |     |

| Partially Inaccessible                                                                | 107 |

| Figure 6-10. Full 16MB Program/Data Memory Map Options                                | 107 |

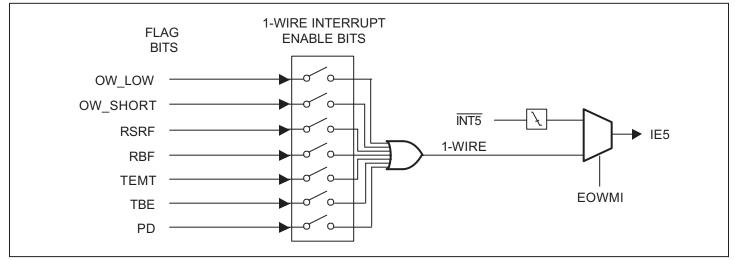

| Figure 9-1. 1-Wire Interrupt Source                                                   | 114 |

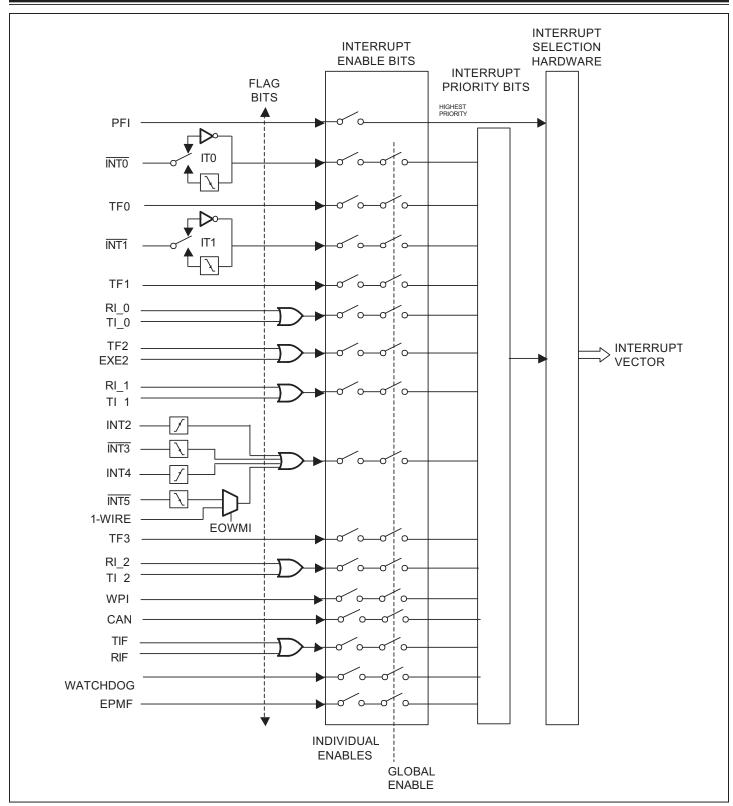

| Figure 9-2. Interrupt Functional Diagram                                              | 115 |

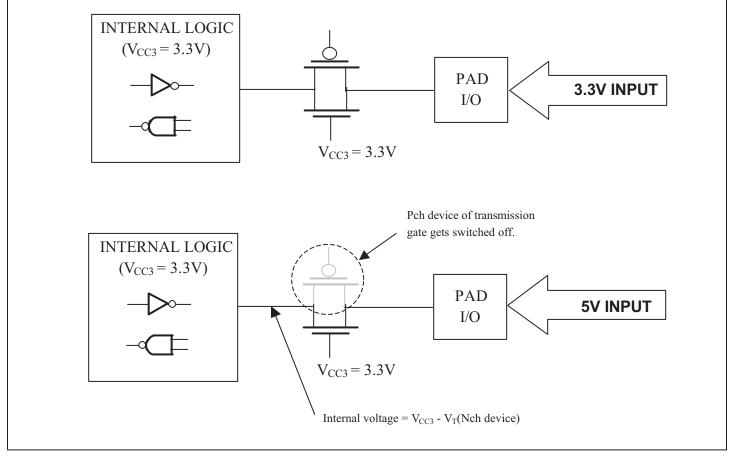

| Figure 10-1. 5V-Tolerant I/O Pad                                                      | 117 |

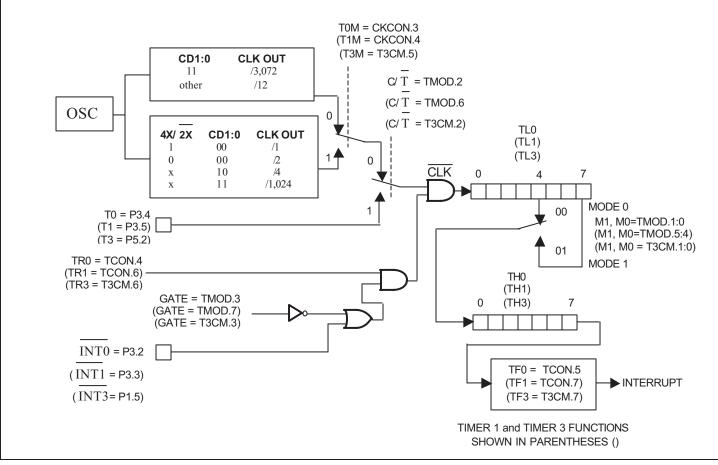

| Figure 11-1. Timers/Counters 0, 1, and 3, Modes 0 and 1                               | 118 |

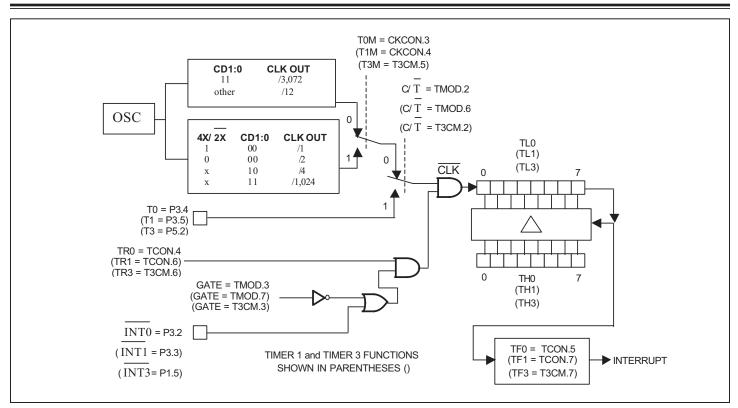

| Figure 11-2. Timers/Counters 0, 1, and 3, Mode 2                                      | 119 |

| Figure 11-3. Timer/Counter 0, Mode 3                                                  | 119 |

| Figure 11-4. Timer/Counter 2 Clock-Out Mode                                           | 120 |

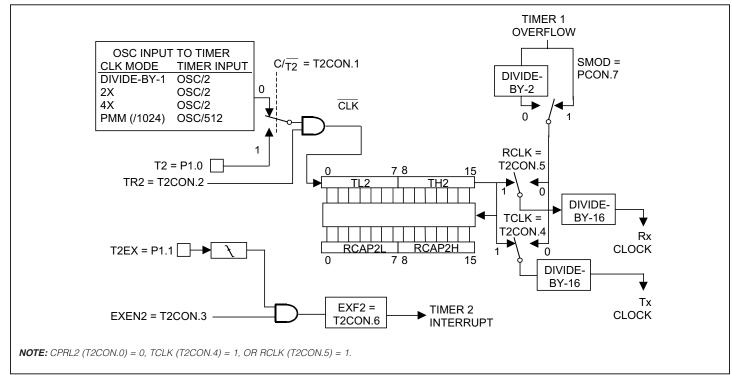

| Figure 11-5. Timer/Counter 2 Baud-Rate Generator Mode                                 | 120 |

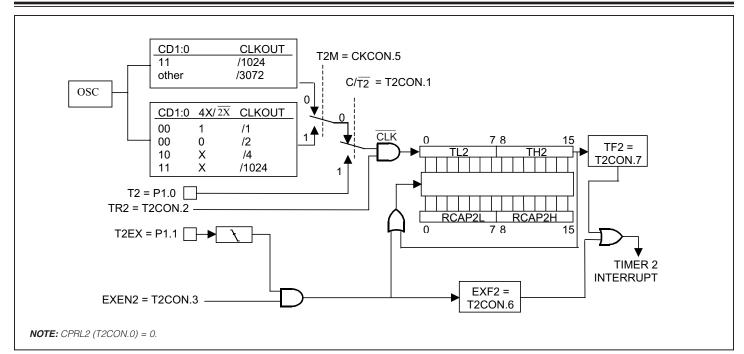

| Figure 11-6. Timer/Counter 2 Autoreload Mode, DCEN = 0                                | 121 |

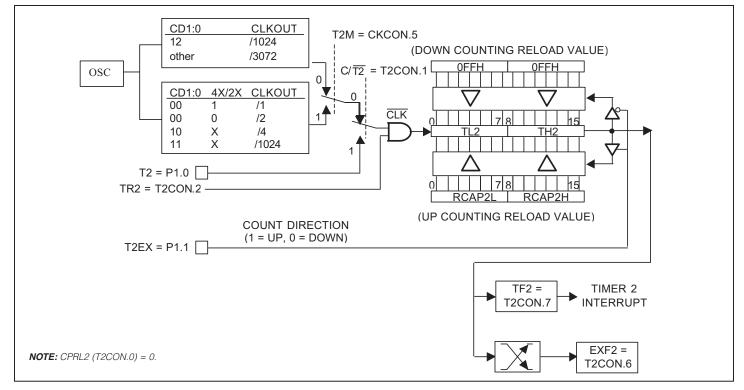

| Figure 11-7. Timer/Counter 2 Autoreload Mode, DCEN = 1                                | 121 |

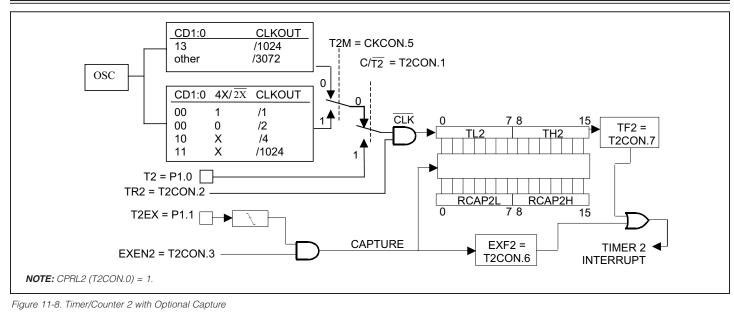

| Figure 11-8. Timer/Counter 2 with Optional Capture                                    | 122 |

| Figure 11-9. Operation of Divide-by-13 Bits                                           | 122 |

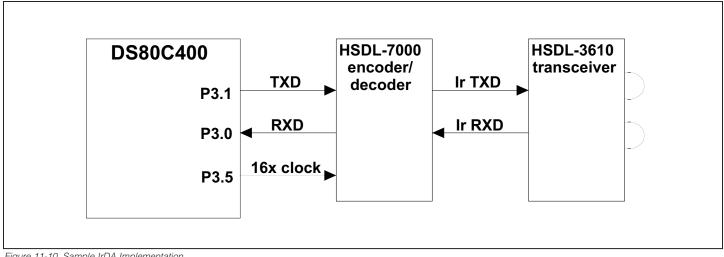

| Figure 11-10. Sample IrDA Implementation                                              |     |

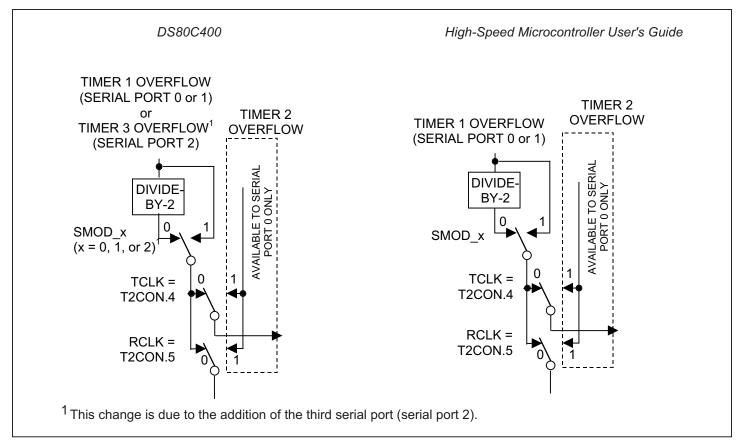

| Figure 12-1. Serial Port Mode 0 Block Diagram Change                                  |     |

| Figure 12-2. Serial Port Mode 2 Block Diagram Change                                  | 126 |

| Figure 12-3. Serial Port Modes 1, 3 Block Diagram Change                              | 128 |

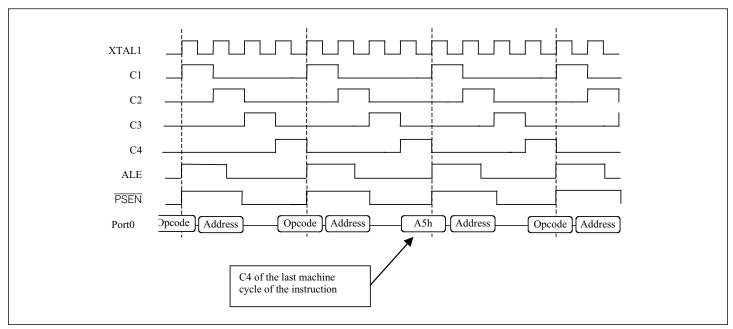

| Figure 17-1. Force Feeding a Breakpoint During An Instruction Other Than MOVC or MOVX | 134 |

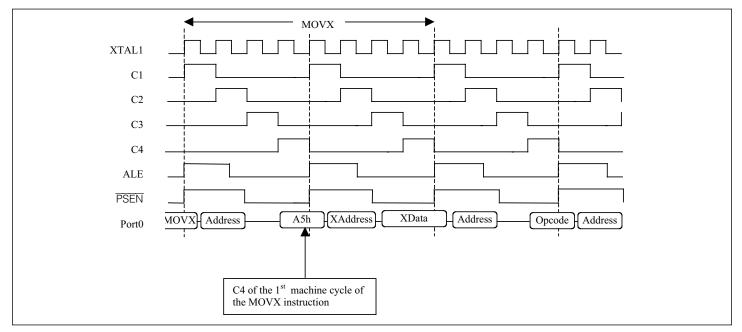

| Figure 17-2. Force Feeding a Breakpoint During a MOVX (2-Cycle)                       | 134 |

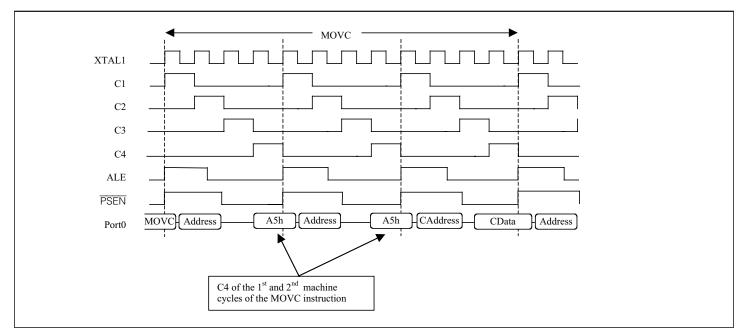

| Figure 17-3. Force Feeding a Breakpoint MOVC                                          | 135 |

| Figure 19-1. CAN 2.0A (Standard) Format                                               | 148 |

| Figure 19-2. CAN 2.0B (Extended) Format                                               | 148 |

| Figure 19-3. Control Field                                                            | 149 |

| Figure 19-4. CRC Field                                                                | 149 |

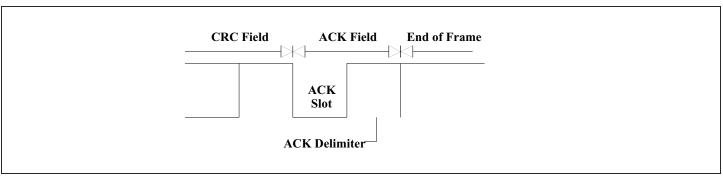

| Figure 19-5. Acknowledge Field                                                        |     |

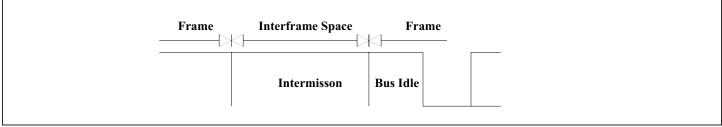

| Figure 19-6. Intermission                                          |      |

|--------------------------------------------------------------------|------|

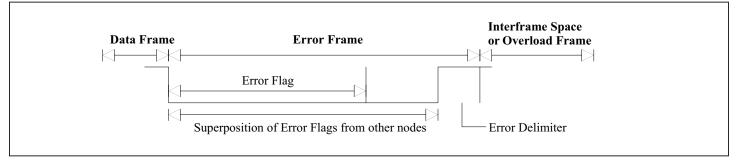

| Figure 19-8. Error Frame                                           |      |

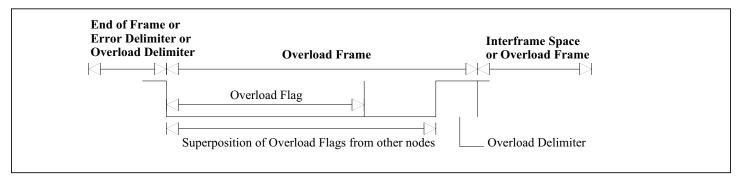

| Figure 19-9. Overload Frame                                        | .151 |

| Figure 19-10. CAN Interrupt Logic                                  | .153 |

| Figure 19-11. Bit Timing                                           |      |

| Figure 21-1. Typical 1-Wire External Hardware Configuration        |      |

| Figure 22-1. Ethernet Controller Block Diagram                     |      |

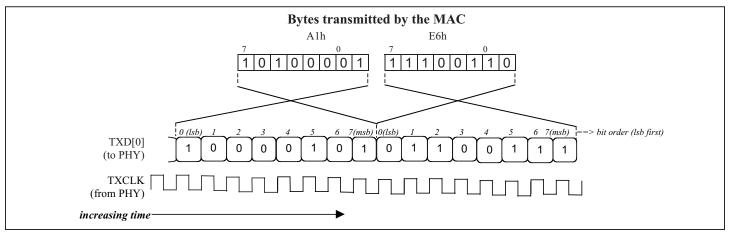

| Figure 22-2. MII Signal Diagram                                    |      |

| Figure 22-3. MII Mode-Byte/Bit Transmit and Receive Order          |      |

| Figure 22-4. ENDEC Signal Diagram                                  |      |

| Figure 22-5. Serial ENDEC Mode-Byte/Bit Transmit and Receive Order |      |

| Figure 22-6. MII Management Frame Format                           |      |

| Figure 22-7. Half-Duplex Transmit Deferral/Collision Handling      |      |

| Figure 22-8. Internal Loopback Mode (MAC Control OM1:0 = 01b)      |      |

| Figure 22-9. External Loopback Mode (MAC Control OM1:0 = 10b)      |      |

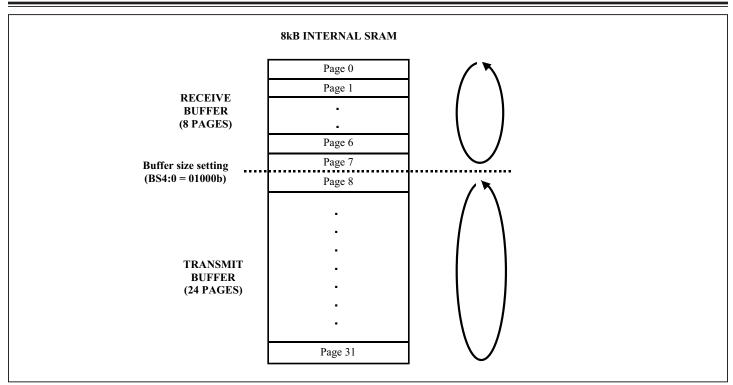

| Figure 22-10. Example 8kB Data Memory Partition                    | .183 |

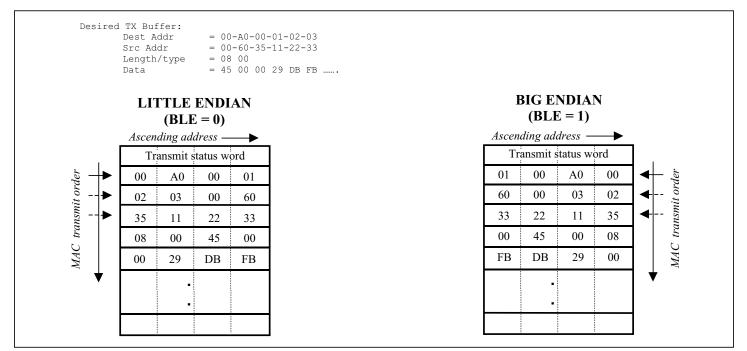

| Figure 22-11. Big/Little-Endian Data Buffers                       | .184 |

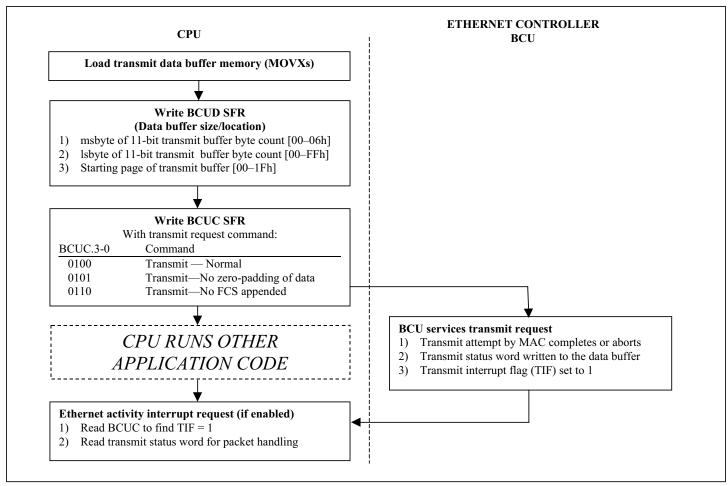

| Figure 22-12. Transmit Flow Diagram                                | .185 |

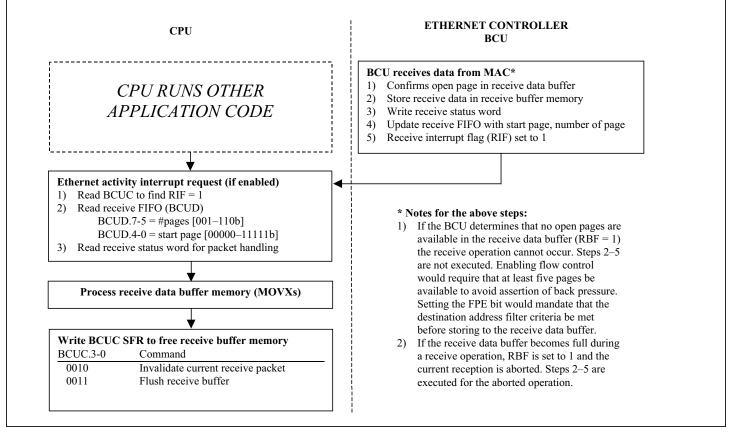

| Figure 22-13. Receive Flow Diagram                                 | .186 |

| Figure 22-14. Wake-Up Frame Filter 0 Programming Example           | .188 |

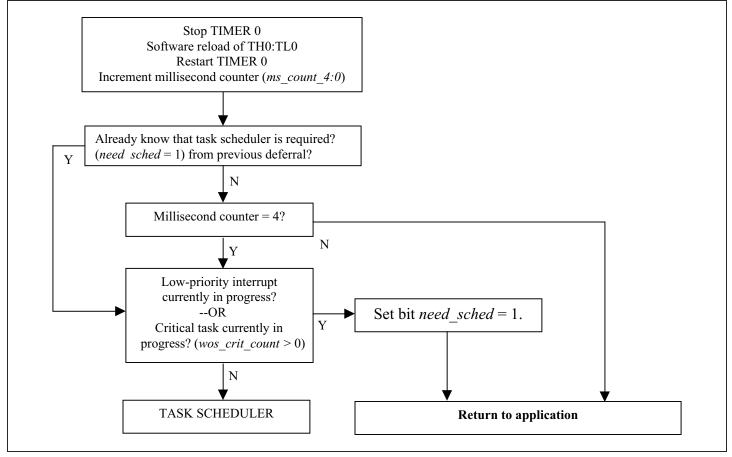

| Figure 23-1. Timer 0 Interrupt Routing (WOS_tick) Flow             | .220 |

## LIST OF TABLES

| 96  |

|-----|

| 96  |

| 100 |

| 101 |

| 101 |

| 101 |

| 102 |

| 108 |

| 108 |

| 118 |

| 24  |

| 124 |

| 125 |

| 26  |

| 27  |

| 28  |

| 65  |

| 170 |

| 171 |

| 173 |

| 174 |

| 181 |

| 187 |

| 217 |

|     |

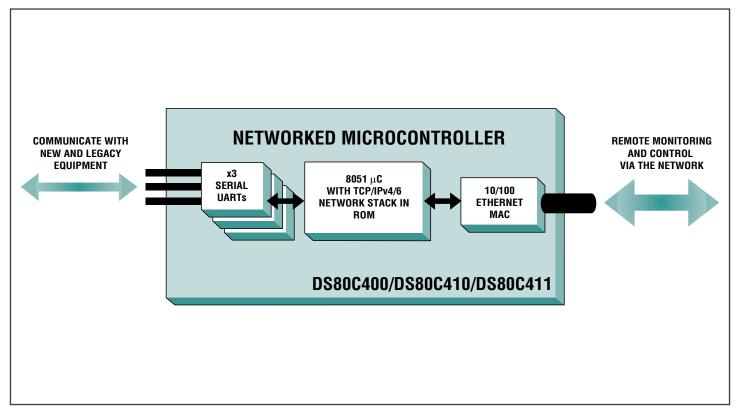

## **ADDENDUM TO SECTION 1: INTRODUCTION**

The DS80C400 is the third-generation microcontroller in the Maxim 8051 family. It is derived from the DS87C520, but adds a full CAN 2.0B controller, a 16/32-bit arithmetic accelerator, a 1-Wire<sup>®</sup> bus master, and an IEEE 802.3-compliant Ethernet media access controller. It incorporates the 8051-compatible high-speed microcontroller core, which has been redesigned to reduce the original 8051's twelve clocks per instruction cycle to four clocks, while using less power. The DS80C400 offers a maximum system clock speed of 75MHz. The DS80C400 also supports a larger program space, data memory space, and stack memory.

The DS80C400 supports three programmable address modes. The 16-bit 8051 address mode of operation is identical with the original 8051 operation. The 24-bit paged address mode is fully compatible with the 8051 operation, but is still capable of supporting a larger memory address range within a multiple page mode configuration. The 24-bit contiguous address mode is supported by a full 24-bit program counter and has eight instructions modified to operate in the 24-bit address range. The 24-bit contiguous address mode requires assembler, compiler, and linker support. The DS80C400 also supports an extended stack in 1kB of internal data RAM.

The DS80C400 provides four data pointers and implements programmable features that are capable of modifying the INC DPTR instruction to actually decrement the active data pointer, automatically toggle the selection of the data pointer, and automatically increment/decrement the select data pointer.

#### **Features**

Seven bidirectional parallel ports Four 16-bit timers/counters with one up/down timer, capture, and baud-rate generation features Power-on reset flag Stop mode exit on interrupts, reset, and CAN bus activity 256 bytes of scratchpad memory Low-power CMOS High-speed, four clocks-per-machine cycle architecture Clock rates: DC to 75MHz (18.75 MIPS) Minimum instruction cycle of 53ns 24-bit program/data address memory access Program counter with selectable 16-bit, 24-bit paged, or 24-bit contiguous mode 16MB external interface 64kB on-chip ROM for bootstrap loader Supports network boot over Ethernet using DHCP and TFTP Full application-accessible TCP/IP network stack Supports IPv4 and IPv6 Implements UDP, TCP, DHCP, ICMP, and IGMP Preemptive, priority-based task scheduler MAC address acquisition from IEEE-registered DS2502-E48 9kB(DS80C400) / 65kB(DS80C410/411) data SRAM Four data pointers with auto INC/DEC function Extended 1kB stack High-speed math accelerator for 16/32-bit multiply and divide calculations One's complement adder 1-Wire bus master Ethernet controller supports 100/10Mbps full-duplex and half-duplex operation Three serial port UARTs with framing error detection and automatic address recognition

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

16 interrupt sources, 6 external and 10 internal with three levels of interrupt nesting and two programmable priority levels Crash-proof, bandgap-referenced power-fail warning; voltage sense reset; and automatic power-up reset timeout Programmable system clock divide control of crystal oscillator. Options include:

Divide-by-1–18.75MHz max. crystal Divide-by-2–37.5MHz max. crystal Divide-by-4–Standard operation Divide-by-1024–Low-speed/power Status register to verify active-interrupt nesting and real-time serial port transmit/receive activity User-selectable multiplexed or nonmultiplexed external address/data interface Programmable watchdog timer Programmable clock-out and reset-out for additional external stand-alone CAN support Full CAN 2.0B controller (DS80C400 and DS80C410): 15 message centers Standard 11-bit or extended 29-bit identification modes Two data byte masks and associated IDs for DeviceNet<sup>™</sup>, SDS, and other higher-layer CAN protocol External transmit disable for autobaud SIESTA low-power mode 100-pin QFP package

## **ADDENDUM TO SECTION 2: ORDERING INFORMATION**

Refer to the individual data sheets for the available versions.

## **ADDENDUM TO SECTION 3: ARCHITECTURE**

The DS80C400 is designed to provide direct compatibility to all of the traditional 80C32 functions, including a 256-byte special function register (SFR), SRAM memory, a third timer (timer 2), and serial port framing-error detection and automatic address recognition. Features on the DS80C400 that are compatible with the DS87C520 include a bandgap-based power monitor for interrupt and reset, timed-access protection, programmable on-board data memory (expanded to 9kB x 8 on the DS80C400, 65kB on the DS80C410/411), programmable system-clock divide ratios, two serial ports, and a programmable watchdog timer. Expanding on these features, the DS80C400 also contains an expanded interrupt capability of 16 interrupts with two programmable interrupt priorities, levels for 15 of the interrupts, and a third-level interrupt priority for power-fail. Additional features include, a math accelerator, a one's complement adder, a 1-Wire bus master, a full CAN 2.0B processor (DS80C400/410), an IEEE 802.3-compliant Ethernet media access controller, a selectable external multiplexed or nonmultiplexed address/data interface, 16-bit, 24-bit paged or 24-bit contiguous addressing operation, and internally decoded chip enables.

The DS80C400 is designed to function similarly to the DS80C390 and run with external program and data memory. The DS80C400 has been designed to operate with an extended 24-bit address map and to support external memories with a minimum of external logic. The DS80C400 also supports an optional extended stack pointer and a 1kB stack memory.

## **CPU Core and CPU Registers**

The CPU core of the DS80C400 executes the same binary-compatible instruction set as that of the 80C32. The principal difference between the core of the DS80C400 and the 80C32 is the number of clocks required to execute specific instructions. The DS80C400 uses a divide-by-4 of the crystal oscillator, and the 80C32 functions with a divide-by-12 of the crystal oscillator. A machine cycle in the DS80C400 defaults to four periods of the crystal oscillator. A machine cycle in the 80C32 is interpreted as 12 cycles of the oscillator. The four MOVX data memory instructions of the DS80C400 have the additional capability of being stretched (external data memory bus access only) from the original data memory access (read or write) time. The MOVX instruction ranges from two machine cycles to 12 machine cycles across eight programmable settings. This MOVX stretch control is user-selectable with the MD2, MD1, and MD0 bits in the clock control register. The ability to do an instruction-based decrement of the DPTR registers is also now supported, through additional control bits in the DPS1 and DPS SFRs.

DeviceNet is a trademark of OpenDeviceNet Vendor Association Inc.

The DS80C400 supports one of three different addressing modes, as selected by software through the AM1 and AM0 bits in the ACON SFR. The microcontroller functions in either the traditional 16-bit address mode, a 24-bit paged address mode, or in a 24-bit contiguous program mode. The microprocessor defaults after a reset to the traditional 16-bit mode, which is identical to the DS80C320 (A23–A16 are forced to 00h). The 24-bit paged address mode is binary code compliant with traditional compilers for the standard 16-bit address range, but allows for up to 16MB of program and 4MB of data memory. A new address page SFR implements an internal bank-switching mechanism in response to a certain set of call/return instructions. The 24-bit contiguous mode requires a 24-bit address compiler that supports contiguous program flow over the entire 24-bit address range by the addition of an operand and/or cycles to eight basic instructions (without the need of bank switching).

The instruction is fetched and sent over the 8-bit internal data bus to the instruction register. The ALU performs math functions, logical operations, and makes comparisons and general decisions. The ALU primarily uses the accumulator and the B register as either the source or destination for most operations.

All peripherals and operations that are not explicit instructions in the DS80C400 are controlled by SFRs. The accumulator is the primary register used in the CPU. It is the source or destination for most operations. The B register is used as the second 8-bit argument in multiply and divide operations. When not used in these operations, the B register can be used as a general-purpose register.

The program status word (PSW) contains a selection of bit flags that include the carry flag, auxiliary carry flag, general-purpose flag, register bank select, overflow flag, and parity flag.

The data pointers are used in accessing program or data memory with the MOVC or MOVX instruction. Two pairs of pointers are provided, simplifying source and destination address tracking when moving data from one memory area to another memory area or to a memory-mapped peripheral.

The DS80C400 provides a stack in either the original 8052 scratchpad area or a 1kB programmable area of the on-chip SRAM. The stack pointer register or register pair, when using the extended 1kB stack, denotes the last used location at the top of the stack.

There are three internal buses, which include a 24-bit address bus and two 8-bit data buses. The address bus provides addresses for op code/operand fetching. The DA data bus is used for addressing SFRs, fetching instructions and operands from external memory, and providing addresses for the internal stack. The DB data bus is used for data exchange between SFRs and the output of all ALU operations.

## **ADDENDUM TO SECTION 4: PROGRAMMING MODEL**

The DS80C400 microprocessor is based on the industry-standard 80C32. The core is an accumulator-based architecture using internal registers for data storage and peripheral control. It executes the standard 8051 instruction set. This section provides a brief description of each architecture feature. Details concerning the programming model, instruction set, and register description are provided in Section 4.

The high-speed microcontroller uses several distinct memory areas. These are registers, program memory, and data memory. Registers serve to control on-chip peripherals and as RAM. Note that registers (on-chip RAM) are separate from data memory. Registers are divided into three categories including directly addressed on-chip RAM, indirectly addressed on-chip RAM, and SFRs. As follows, the program and data memory areas are discussed under *Memory Map*, and the registers are discussed under *Registers Map*.

## **Memory Map**

The DS80C400 microcontroller defaults to the memory compatibility of the 8051. This device can address up to 1kB of on-chip SRAM. In addition to the standard 16-bit address mode, the DS80C400 can operate in 24-bit paged or 24-bit contiguous address mode. The DS80C400 has four internal memory areas: 256 bytes of scratchpad RAM, 9kB(DS80C400) / 65kB(DS80C410/411) SRAM, 256 bytes of RAM reserved for the CAN message centers, and 64kB of embedded ROM firmware. A 22-bit address bus and an 8-bit data bus operating in multiplexed or demultiplexed mode can address 16MB of external memory. By configuring the SFRs, eight available chipenable pins are used to access 16MB of external program memory. Also, 4MB of external data memory is accessible by configuring four peripheral, chip-enable bits in the SFRs. The addresses of the program and data segments can overlap since they are accessed in different ways. Program memory is fetched by the microprocessor automatically. These addresses are never written by software. There is one instruction (MOVC) that is used to explicitly read the program area. This is commonly used to read lookup tables. The data memory area is accessed explicitly using the MOVX instruction. This instruction provides multiple ways of specifying the target address. In addition, the DS80C400 can be configured to permit a merged von Neumann-style program/data memory space. Detailed descriptions of the memory mapping alternatives are discussed in a separate section of this user's guide supplement.

## **Register Map**

The register map is separate from the program and data memory areas mentioned above. A separate class of instructions is used to access the registers. There are 256 potential register location values. In practice, the high-speed microcontroller has 256 bytes of scratchpad RAM and up to 128 SFRs. This is possible since the upper 128 scratchpad RAM locations can only be accessed indirectly. That is, the contents of a working register, described later, designate the RAM location. Thus, a direct reference to one of the upper 128 locations must be an SFR access. Direct RAM is reached at locations 0 to 7Fh (0–127). SFRs are accessed directly between 80h and FFh (128–255). The RAM locations between 128 and 255 can be reached through an indirect reference to those locations.

Scratchpad RAM is available for general-purpose data storage. It is commonly used in place of off-chip RAM when the total data contents are small. When off-chip RAM is needed, the scratchpad area still provides the fastest general-purpose access. Within the 256 bytes of RAM, there are several special-purpose areas, which are described as follows.

#### **Bit-Addressable Locations**

In addition to direct register access, some individual bits in both the RAM and SFR area are also accessible. In the scratchpad RAM area, registers 20h to 2Fh are bit addressable. This provides 128 (16  $\times$  8) individual bits available to software. The type of instruction distinguishes a bit access from a full register access. In the SFR area, any register location ending in a 0 or 8 is bit addressable.

#### **Working Registers**

As part of the lower 128 bytes of RAM, there are four banks of general-purpose working registers, each bank containing registers R0–R7. The bank is selected by bits in the program status word register. Since there are four banks, the currently selected bank is used by any instruction using R0–R7. This allows software to change context by switching banks. The working registers also allow their contents to be used for indirect addressing of the upper 128 bytes of RAM. Thus, an instruction can designate the value stored in R0, for example, to address the upper RAM. This value might be the result of another calculation.

#### Stack

Another use of the scratchpad area is for the programmer's stack. This area is selected using the stack pointer (SP: 81h) SFR. Whenever a call or interrupt is invoked, the return address is placed on the stack. It is also available to the programmer for variables, etc. The stack pointer defaults to 07h on reset, but can be relocated as needed. A convenient location would be the upper RAM area (> 7Fh), since this is only available indirectly. The SP points to the last used value. Therefore, the next value placed on the stack is put at SP + 1. Each PUSH or CALL increments the SP by the appropriate value. Each POP or RET decrements, as well.

The DS80C400 supports an optional 10-bit (1kB) stack. This greatly increases programming efficiency and allows the device to support large programs. When enabled by setting the stack address (SA) bit in the ACON register, 1kB of the internal SRAM is allocated for use as the stack. The 10-bit address is formed by concatenating the lower 2 bits of the extended stack pointer (ESP: 9Bh) and the 8-bit stack pointer (SP: 81h). The exact address of the 1kB is dependent on the setting of the IDM1-0 bits.

### **Special-Function Register Maps**

Most of the unique features of the high-speed microcontroller family are controlled by bits in SFRs located in unused locations in the 8052 SFR map. This allows for increased functionality, while maintaining complete instruction set compatibility. The SFRs reside in register locations 80h–FFh and are accessed using direct addressing. SFRs that end in 0h or 8h are bit addressable.

The Special Function Register Map table indicates the names and locations of the SFRs used by the DS80C400. The Special Function Register Location table shows individual bits in those registers. Bits protected by the timed-access function are shaded. The Special Function Register Reset Values table indicates the reset state of all SFR bits. Following these tables is a complete description of DS80C400 SFRs that are new to the 8051 architecture or have new or modified functionality.

## **Special-Function Register Map**

| START<br>ADDRESS |       |        |        | SFR    | NAMES  |        |        |         | END<br>ADDRESS |

|------------------|-------|--------|--------|--------|--------|--------|--------|---------|----------------|

| 80               | P4    | SP     | DPL    | DPH    | DPL1   | DPH1   | DPS    | PCON    | 87             |

| 88               | TCON  | TMOD   | TLO    | TL1    | THO    | TH1    | CKCON  |         | 8F             |

| 90               | P1    | EXIF   | P4CNT  | DPX    |        | DPX1   | C0RMS0 | CORMS1  | 97             |

| 98               | SCON0 | SBUF0  |        | ESP    | AP     | ACON   | COTMA0 | C0TMA1  | 9F             |

| A0               | P2    | P5     | P5CNT  | COC    | COS    | COIR   | COTE   | CORE    | A7             |

| A8               | IE    | SADDR0 | SADDR1 | C0M1C  | C0M2C  | C0M3C  | C0M4C  | C0M5C   | AF             |

| B0               | P3    | P6     | P6CNT  | C0M6C  | C0M7C  | C0M8C  | C0M9C  | C0M10C  | B7             |

| B8               | IP    | SADEN0 | SADEN1 | C0M11C | C0M12C | C0M13C | C0M14C | C0M15C  | BF             |

| CO               | SCON1 | SBUF1  |        |        | PMR    | STATUS | MCON   | TA      | C7             |

| C8               | T2CON | T2MOD  | RCAP2L | RCAP2H | TL2    | TH2    | COR    |         | CF             |

| D0               | PSW   | MCNT0  | MCNT1  | MA     | MB     | MC     | MCON1  | MCON2   | D7             |

| D8               | WDCON | SADDR2 | BPA1   | BPA2   | BPA3   |        |        |         | DF             |

| EO               | ACC   | OCAD   |        | CSRD   | CSRA   | EBS    | BCUD   | BCUC    | E7             |

| E8               | EIE   |        | MXAX   | DPX2   |        | DPX3   | OWMAD  | OWMDR   | EF             |

| F0               | В     | SADEN2 | DPL2   | DPH2   | DPL3   | DPH3   | DPS1   | STATUS1 | F7             |

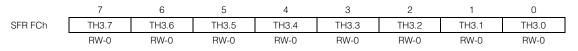

| F8               | EIP   | P7     |        | TL3    | TH3    | T3CM   | SCON2  | SBUF2   | FF             |

## **Special-Function Register Location**

| REGISTER | BIT 7  | BIT 6 | BIT 5   | BIT 4   | BIT 3   | BIT 2   | BIT 1   | BIT 0   | ADDRESS |

|----------|--------|-------|---------|---------|---------|---------|---------|---------|---------|

| P4       |        |       |         |         |         |         |         |         | 80h     |

| SP       |        |       |         |         |         |         |         |         | 81h     |

| DPL      |        |       |         |         |         |         |         |         | 82h     |

| DPH      |        |       |         |         |         |         |         |         | 83h     |

| DPL1     |        |       |         |         |         |         |         |         | 84h     |

| DPH1     |        |       |         |         |         |         |         |         | 85h     |

| DPS      | ID1    | ID0   | TSL     | AID     | SEL1    | —       | —       | SEL     | 86h     |

| PCON     | SMOD_0 | SMOD0 | OFDF    | OFDE    | GF1     | GF0     | STOP    | IDLE    | 87h     |

| TCON     | TF1    | TR1   | TF0     | TR0     | IE1     | IT1     | IEO     | ITO     | 88h     |

| TMOD     | GATE   | C/T   | M1      | MO      | GATE    | C/T     | M1      | MO      | 89h     |

| TLO      |        |       |         |         |         |         |         |         | 8Ah     |

| TL1      |        |       |         |         |         |         |         |         | 8Bh     |

| TH0      |        |       |         |         |         |         |         |         | 8Ch     |

| TH1      |        |       |         |         |         |         |         |         | 8Dh     |

| CKCON    | WD1    | WD0   | T2M     | T1M     | TOM     | MD2     | MD1     | MD0     | 8Eh     |

| P1       |        |       |         |         |         |         |         |         | 90h     |

| EXIF     | IE5    | IE4   | IE3     | IE2     | CKRY    | RGMD    | RGSL    | BGS     | 91h     |

| P4CNT    | —      | —     | P4CNT.5 | P4CNT.4 | P4CNT.3 | P4CNT.2 | P4CNT.1 | P4CNT.0 | 92h     |

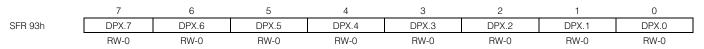

| DPX      |        |       |         |         |         |         |         |         | 93h     |

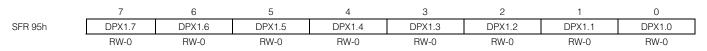

| DPX1     |        |       |         |         |         |         |         |         | 95h     |

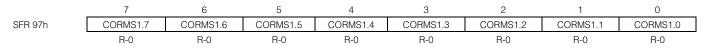

| CORMS0*  |        |       |         |         |         |         |         |         | 96h     |

| CORMS1*  |        |       |         |         |         |         |         |         | 97h     |

## Special-Function Register Location (continued)

| REGISTER    | BIT 7    | BIT 6    | BIT 5   | BIT 4   | BIT 3   | BIT 2   | BIT 1   | BIT 0     | ADDRESS     |

|-------------|----------|----------|---------|---------|---------|---------|---------|-----------|-------------|

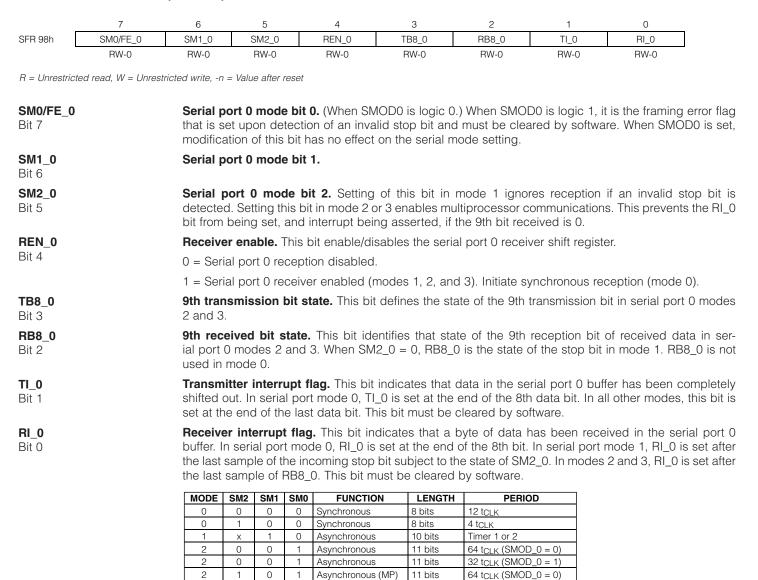

| SCON0       | SM0/FE_0 | SM1_0    | SM2_0   | REN_0   | TB8_0   | RB8_0   | TI_0    | RI_0      | 98h         |

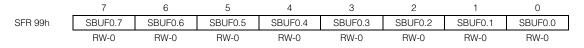

| SBUF0       |          |          |         |         |         |         |         |           | 99h         |

| ESP         | _        | _        | _       |         |         | _       | ESP.1   | ESP.0     | 9Bh         |

| AP          |          |          |         |         |         |         |         |           | 9Ch         |

| ACON        | _        | _        | MROM    | BPME    | BROM    | SA      | AM1     | AM0       | 9Dh         |

| C0TMA0*     |          |          |         |         |         |         |         |           | 9Eh         |

| C0TMA1*     |          |          |         |         |         |         |         |           | 9Fh         |

| P2          |          |          |         |         |         |         |         |           | A0h         |

| P5          |          |          |         |         |         |         |         |           | A1h         |

| P5CNT*      | _        | CANOBA   | _       |         | C0_I/O  | P5CNT.2 | P5CNT.1 | P5CNT.0   | A2h         |

| C0C*        | ERIE     | STIE     | PDE     | SIESTA  | CRST    | AUTOB   | ERCS    | SWINT     | A3h         |

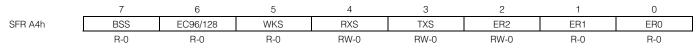

| C0S*        | BSS      | EC96/128 | WKS     | RXS     | TXS     | ER2     | ER1     | ER0       | A4h         |

| C0IR*       | INTIN7   | INTIN6   | INTIN5  | INTIN4  | INTIN3  | INTIN2  | INTIN1  | INTINO    | A5h         |

| COTE*       |          | -        | -       |         | -       |         |         |           | A6h         |

| CORE*       |          |          |         |         |         |         |         |           | A7h         |

| IE          | EA       | ES1      | ET2     | ES0     | ET1     | EX1     | ETO     | EX0       | A8h         |

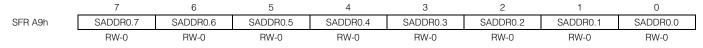

| SADDR0      |          | -        |         |         |         |         |         |           | A9h         |

| SADDR1      |          |          |         |         |         |         |         |           | AAh         |

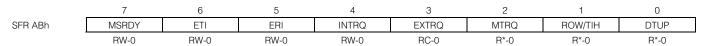

| COM1C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | ABh         |

| COM2C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | ACh         |

| COM3C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | ADh         |

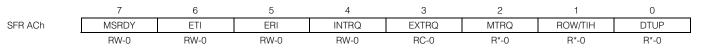

| COM4C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | AEh         |

| C0M5C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | AFh         |

| P3          |          |          |         |         |         |         |         |           | B0h         |

| P6          |          |          |         |         |         |         |         |           | Bih         |

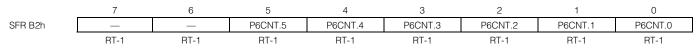

| P6CNT       | _        | _        | P6CNT.5 | P6CNT.4 | P6CNT.3 | P6CNT.2 | P6CNT.1 | P6CNT.0   | B2h         |

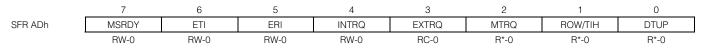

| COM6C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | B3h         |

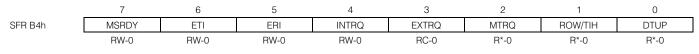

| COM7C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | B4h         |

| COM8C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | B5h         |

| COM9C*      | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | B6h         |

| COM10C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | B7h         |

| IP          | _        | PS1      | PT2     | PSO     | PT1     | PX1     | PTO     | PX0       | B8h         |

| SADENO      |          |          |         |         |         |         |         |           | B9h         |

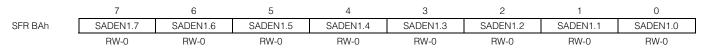

| SADEN1      |          |          |         |         |         |         |         |           | BAh         |

| COM11C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | BBh         |

| COM12C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | BCh         |

| COM13C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | BDh         |

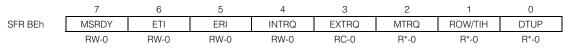

| COM14C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | BEh         |

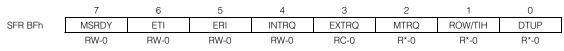

| COM15C*     | MSRDY    | ETI      | ERI     | INTRQ   | EXTRQ   | MTRQ    | ROW/TIH | DTUP      | BFh         |

| SCON1       | SM0/FE_1 | SM1_1    | SM2_1   | REN_1   | TB8_1   | RB8_1   | TI_1    | RI_1      | C0h         |

| SBUF1       |          | 0001_1   | 0002_1  |         | 100_1   | 1.50_1  |         |           | C0h         |

| PMR         | CD1      | CD0      | SWB     | СТМ     | 4X/2X   | ALEOFF  | _       | _         | C4h         |

| STATUS      | PIP      | HIP      | LIP     |         | SPTA1   | SPRA1   | SPTA0   | <br>SPRA0 | C4II<br>C5h |

| MCON*       | IDM1     | IDM0     | CMA     |         | PDCE3   | PDCE2   | PDCE1   | PDCE0     | C5h         |

| TA          |          |          | OWA     |         | TUCLS   | TOOLZ   | TUCLI   | - I DOLU  | Con<br>C7h  |

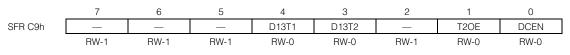

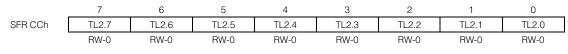

| TA<br>T2CON | TF2      | EXF2     | RCLK    | TCLK    | EXEN2   | TR2     | C/T2    | CP/RL2    | C7h<br>C8h  |

| 120011      | 11-2     | LAFZ     | NOLIN   | D13T1   | D13T2   | 102     | T2OE    | UT/NLZ    | 0011        |

| REGISTER | BIT 7    | BIT 6 | BIT 5 | BIT 4  | BIT 3  | BIT 2 | BIT 1 | BIT 0  | ADDRESS |

|----------|----------|-------|-------|--------|--------|-------|-------|--------|---------|

| RCAP2L   |          |       |       |        |        |       |       |        | CAh     |

| RCAP2H   |          |       |       |        |        |       |       |        | CBh     |

| TL2      |          |       |       |        |        |       |       |        | CCh     |

| TH2      |          |       |       |        |        |       |       |        | CDh     |

| COR*     | IRDACK   | —     | —     | C0BPR7 | C0BPR6 | COD1  | COD0  | XCLKOE | CEh     |

| PSW      | CY       | AC    | F0    | RS1    | RS0    | OV    | F1    | Р      | D0h     |

| MCNT0    | LSHIFT   | CSE   | SCE   | MAS4   | MAS3   | MAS2  | MAS1  | MAS0   | D1h     |

| MCNT1    | MST      | MOF   | SCB   | CLM    | _      | _     | _     | _      | D2h     |

| MA       |          |       |       |        |        |       |       |        | D3h     |

| MB       |          |       |       |        |        |       |       |        | D4h     |

| MC       |          |       |       |        |        |       |       |        | D5h     |

| MCON1*   | IRAMD    | PRAME | _     |        | PDCE7  | PDCE6 | PDCE5 | PDCE4  | D6h     |

| MCON2*   | WPIF     | WPR2  | WPR1  | WPR0   | WPE3   | WPE2  | WPE1  | WPE0   | D7h     |

| WDCON    | SMOD_1   | POR   | EPF1  | PF1    | WDIF   | WTRF  | EWT   | RWT    | D8h     |

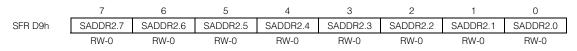

| SADDR2   |          |       |       |        |        |       |       |        | D9h     |

| BPA1     |          |       |       |        |        |       |       |        | DAh     |

| BPA2     |          |       |       |        |        |       |       |        | DBh     |

| BPA3     |          |       |       |        |        |       |       |        | DCh     |

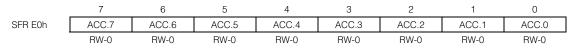

| ACC      |          |       |       |        |        |       |       |        | E0h     |

| OCAD     |          |       |       |        |        |       |       |        | E1h     |

| CSRD     |          |       |       |        |        |       |       |        | E3h     |

| CSRA     |          |       |       |        |        |       |       |        | E4h     |

| EBS      | FPE      | RBF   | _     | BS4    | BS3    | BS2   | BS1   | BS0    | E5h     |

| BCUD     |          |       |       |        |        |       |       |        | E6h     |

| BCUC     | BUSY     | EPMF  | TIF   | RIF    | BC3    | BC2   | BC1   | BC0    | E7h     |

| EIE*     | EPMIE    | COIE  | EAIE  | EWDI   | EWPI   | ES2   | ET3   | EX2-5  | E8h     |

| MXAX     |          |       |       |        |        |       |       |        | EAh     |

| DPX2     |          |       |       |        |        |       |       |        | EBh     |

| DPX3     |          |       |       |        |        |       |       |        | EDh     |

| OWMAD    | _        | —     | —     | —      | —      | A2    | A1    | AO     | EEh     |

| OWMDR    |          |       |       |        |        |       |       |        | EFh     |

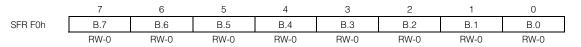

| В        |          |       |       |        |        |       |       |        | F0h     |

| SADEN2   |          |       |       |        |        |       |       |        | F1h     |

| DPL2     |          |       |       |        |        |       |       |        | F2h     |

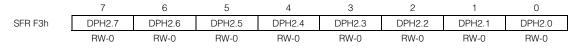

| DPH2     |          |       |       |        |        |       |       |        | F3h     |

| DPL3     |          |       |       |        |        |       |       |        | F4h     |

| DPH3     |          |       |       |        |        |       |       |        | F5h     |

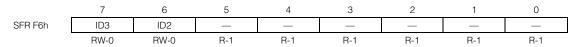

| DPS1     | ID3      | ID2   | _     | _      | _      | _     | _     | _      | F6h     |

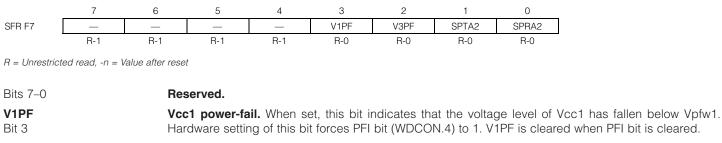

| STATUS1  |          |       | _     |        | V1PF   | V3PF  | SPTA2 | SPRA2  | F7h     |

| EIP*     | EPMIP    | COIP  | EAIP  | PWDI   | PWPI   | PS2   | PT3   | PX2-5  | F8h     |