# MAXQ7665/MAXQ7666 USER'S GUIDE

For the modulo increment or decrement operation, the selected range of bits in AP are incremented or decremented. However, if these bits roll over or under, they simply wrap around without affecting the remaining bits in the accumulator pointer. So, the operations can be defined as follows:

- Increment modulo 2: AP = AP[3:1] + ((AP[0] + 1) mod 2)

- Decrement modulo 2: AP = AP[3:1] + ((AP[0] 1) mod 2)

- Increment modulo 4: AP = AP[3:2] + ((AP[1:0] + 1) mod 4)

- Decrement modulo 4: AP = AP[3:2] + ((AP[1:0] 1) mod 4)

- Increment modulo 8: AP = AP[3] + ((AP[2:0] + 1) mod 8)

- Decrement modulo 8: AP = AP[3] + ((AP[2:0] 1) mod 8)

- Increment modulo 16: AP = (AP + 1) mod 16

- Decrement modulo 16: AP = (AP 1) mod 16

For this example, assume that all 16 accumulator registers are initially set to zero.

| move | AP, #02h  | ; | sele | ct A[2]  | as acti   | ve accu  | mulator |

|------|-----------|---|------|----------|-----------|----------|---------|

| move | APC, #02h | ; | auto | -increme | ent AP[ 1 | :0] modu | ulo 4   |

|      |           | ; | AP   | A[ 0]    | A[ 1]     | A[ 2]    | A[ 3]   |

|      |           | ; | 02   | 0000     | 0000      | 0000     | 0000    |

| add  | #01h      | ; | 03   | 0000     | 0000      | 0001     | 0000    |

| add  | #02h      | ; | 00   | 0000     | 0000      | 0001     | 0002    |

| add  | #03h      | ; | 01   | 0003     | 0000      | 0001     | 0002    |

| add  | #04h      | ; | 02   | 0003     | 0004      | 0001     | 0002    |

| add  | #05h      | ; | 03   | 0003     | 0004      | 0006     | 0002    |

|      |           |   |      |          |           |          |         |

### 1.3.5.3 ALU Operations Using the Active Accumulator and a Source

The following arithmetic and logical operations can use any register or immediate value as a source. The active accumulator Acc is always used as the second operand and the implicit destination. Also, Acc may not be used as the source for any of these operations.

| add<br>addc | A[ 4]<br>#32h           | ; Acc = Acc + A[4]<br>; Acc = Acc + 0032h + Carry                                       |    |

|-------------|-------------------------|-----------------------------------------------------------------------------------------|----|

| subb        | A[ 15]<br>A[ 1]<br>#00h | ; Acc = Acc - A[15]<br>; Acc = Acc - A[1] - Carry<br>; If (Acc == 0000h), set Equals fl | ag |

|             | A[ 0]<br>#55h           | ; Acc = Acc AND A[ 0]<br>; Acc = Acc OR #0055h                                          |    |

| xor         | A[ 1]                   | ; Acc = Acc XOR A[ 1]                                                                   |    |

# SECTION 1: MAXQ7665/MAXQ7666 CORE ARCHITECTURE

This section contains the following information:

| 1.1 Overview                                                 |

|--------------------------------------------------------------|

| 1.1.1 References                                             |

| 1.1.2 Instruction Set                                        |

| 1.1.3 Harvard Memory Architecture1-6                         |

| 1.1.4 Register Space                                         |

| 1.2 Architecture                                             |

| 1.2.1 Instruction Decoding1-8                                |

| 1.2.2 Register Space                                         |

| 1.2.3 Memory Organization1-11                                |

| 1.2.3.1 Program Memory1-11                                   |

| 1.2.3.2 Utility ROM                                          |

| 1.2.3.3 Data Memory                                          |

| 1.2.3.4 Stack Memory1-15                                     |

| 1.2.3.5 Pseudo-Von Neumann Memory Mapping                    |

| 1.2.3.6 Pseudo-Von Neumann Memory Access                     |

| 1.2.3.7 Data Alignment                                       |

| 1.2.3.8 Memory Management Unit1-17                           |

| 1.2.3.9 Program and Data Memory Mapping Example 1: MAXQ7665B |

| 1.2.3.10 Program and Data Memory Mapping Example 2: MAXQ7666 |

| 1.2.4 Interrupts                                             |

| 1.2.4.1 Servicing Interrupts1-23                             |

| 1.2.4.2 Interrupt System Operation1-24                       |

| 1.2.4.3 Synchronous vs. Asynchronous Interrupt Sources       |

| 1.2.4.4 Interrupt Prioritization by Software                 |

| 1.2.4.5 Interrupt Exception Window                           |

| 1.2.4.6 MAXQ7665/MAXQ7666 Interrupt Sources                  |

| 1.3 Programming                                              |

| 1.3.1 Addressing Modes                                       |

| 1.3.2 Prefixing Operations1-29                               |

| 1.3.3 Reading and Writing Registers1-30                      |

| 1.3.3.1 Loading an 8-Bit Register with an Immediate Value                              | 1-30 |

|----------------------------------------------------------------------------------------|------|

| 1.3.3.2 Loading a 16-Bit Register with a 16-Bit Immediate Value                        | 1-30 |

| 1.3.3.3 Moving Values Between Registers of the Same Size                               | 1-30 |

| 1.3.3.4 Moving Values Between Registers of Different Sizes                             | 1-30 |

| 1.3.3.4.1 8-Bit Destination $\leftarrow$ Low Byte (16-Bit Source)                      | 1-31 |

| 1.3.3.4.2 8-Bit Destination $\leftarrow$ High Byte (16-Bit Source)                     | 1-31 |

| 1.3.3.4.3 16-Bit Destination $\leftarrow$ Concatenation (8-Bit Source, 8-Bit Source) . | 1-31 |

| 1.3.3.4.4 Low (16-Bit Destination) $\leftarrow$ 8-Bit Source                           | 1-31 |

| 1.3.3.4.5 High (16-Bit Destination) $\leftarrow$ 8-Bit Source                          | 1-31 |

| 1.3.4 Reading and Writing Register Bits                                                | 1-32 |

| 1.3.5 Using the Arithmetic and Logic Unit                                              | 1-32 |

| 1.3.5.1 Selecting the Active Accumulator                                               | 1-32 |

| 1.3.5.2 Enabling Auto-Increment and Auto-Decrement                                     | 1-32 |

| 1.3.5.3 ALU Operations Using the Active Accumulator and a Source                       | 1-34 |

| 1.3.5.4 ALU Operations Using Only the Active Accumulator                               | 1-35 |

| 1.3.5.5 ALU Bit Operations Using Only the Active Accumulator                           | 1-35 |

| 1.3.5.6 Example: Adding Two 4-Byte Numbers Using Auto-Increment                        | 1-35 |

| 1.3.6 Processor Status Flag Operations                                                 | 1-35 |

| 1.3.6.1 Sign Flag                                                                      | 1-35 |

| 1.3.6.2 Zero Flag                                                                      | 1-36 |

| 1.3.6.3 Equals Flag                                                                    | 1-36 |

| 1.3.6.4 Carry Flag                                                                     | 1-36 |

| 1.3.6.5 Overflow Flag                                                                  | 1-37 |

| 1.3.7 Controlling Program Flow                                                         | 1-37 |

| 1.3.7.1 Obtaining the Next Execution Address                                           | 1-37 |

| 1.3.7.2 Unconditional Jumps                                                            | 1-37 |

| 1.3.7.3 Conditional Jumps                                                              | 1-38 |

| 1.3.7.4 Calling Subroutines                                                            | 1-38 |

| 1.3.7.5 Looping Operations                                                             | 1-38 |

| 1.3.7.6 Conditional Returns                                                            | 1-39 |

| 1.3.8 Handling Interrupts                                                              | 1-39 |

| 1.3.8.1 Conditional Return from Interrupt                                              | 1-40 |

| 1.3.9 Accessing the Stack                                                              | 1-40 |

| 1.3.10 Accessing Data Memory                          | 1-41 |

|-------------------------------------------------------|------|

| 1.4 System Register Descriptions                      | 1-43 |

| 1.4.1 Accumulator Pointer Register (AP)               | 1-46 |

| 1.4.2 Accumulator Pointer Control Register (APC)      | 1-46 |

| 1.4.3 Processor Status Flags Register (PSF)           | 1-47 |

| 1.4.4 Interrupt and Control Register (IC)             | 1-48 |

| 1.4.5 Interrupt Mask Register (IMR)                   | 1-48 |

| 1.4.6 System Control Register (SC)                    | 1-49 |

| 1.4.7 Interrupt Identification Register (IIR)         | 1-50 |

| 1.4.8 System Clock Control Register (CKCN)            | 1-50 |

| 1.4.9 Watchdog Timer Control Register (WDCN)          | 1-51 |

| 1.4.10 Accumulator n Register (A[n])                  | 1-51 |

| 1.4.11 Prefix Register (PFX[n])                       | 1-52 |

| 1.4.12 Instruction Pointer Register (IP)              | 1-53 |

| 1.4.13 Stack Pointer Register (SP)                    | 1-53 |

| 1.4.14 Interrupt Vector Register (IV)                 | 1-54 |

| 1.4.15 Loop Counter 0 Register (LC[0])                | 1-54 |

| 1.4.16 Loop Counter 1 Register (LC[1])                | 1-55 |

| 1.4.17 Frame Pointer Offset Register (OFFS)           | 1-55 |

| 1.4.18 Data Pointer Control Register (DPC)            | 1-56 |

| 1.4.19 General Register (GR)                          | 1-57 |

| 1.4.20 General Register Low Byte (GRL)                | 1-57 |

| 1.4.21 Frame Pointer Base Register (BP)               | 1-58 |

| 1.4.22 General Register Byte-Swapped (GRS)            | 1-58 |

| 1.4.23 General Register High Byte (GRH)               | 1-59 |

| 1.4.24 General Register Sign Extended Low Byte (GRXL) | 1-59 |

| 1.4.25 Frame Pointer Register (FP)                    | 1-60 |

| 1.4.26 Data Pointer 0 Register (DP[0])                | 1-60 |

| 1.4.27 Data Pointer 1 Register (DP[1])                |      |

| 1.5 Peripheral Register Modules                       | 1-61 |

# **LIST OF FIGURES**

| Figure 1-1. MAXQ7665/MAXQ7666 Block Diagram                            | .1-5  |

|------------------------------------------------------------------------|-------|

| Figure 1-2. MAXQ7665/MAXQ7666 Transport-Triggered Architecture         | .1-7  |

| Figure 1-3. Instruction Word Format                                    | .1-8  |

| Figure 1-4. Pseudo-Von Neumann Memory Map (MAXQ7665/MAXQ7666 Default)  | .1-16 |

| Figure 1-5. CDA Functions (Word Access Mode)                           | .1-18 |

| Figure 1-6. CDA Functions (Byte Access Mode)                           | .1-19 |

| Figure 1-7. MAXQ7665B Memory Map When Executing from Application Flash | .1-20 |

| Figure 1-8. MAXQ7665B Memory Map When Executing from Utility ROM       | .1-21 |

| Figure 1-9. MAXQ7665B Memory Map When Executing from Data SRAM         | .1-21 |

| Figure 1-10. MAXQ7666 Memory Map When Executing from Application Flash | .1-22 |

| Figure 1-11. MAXQ7666 Memory Map When Executing from Utility ROM       | .1-22 |

| Figure 1-12. MAXQ7666 Memory Map When Executing from Data RAM          | .1-23 |

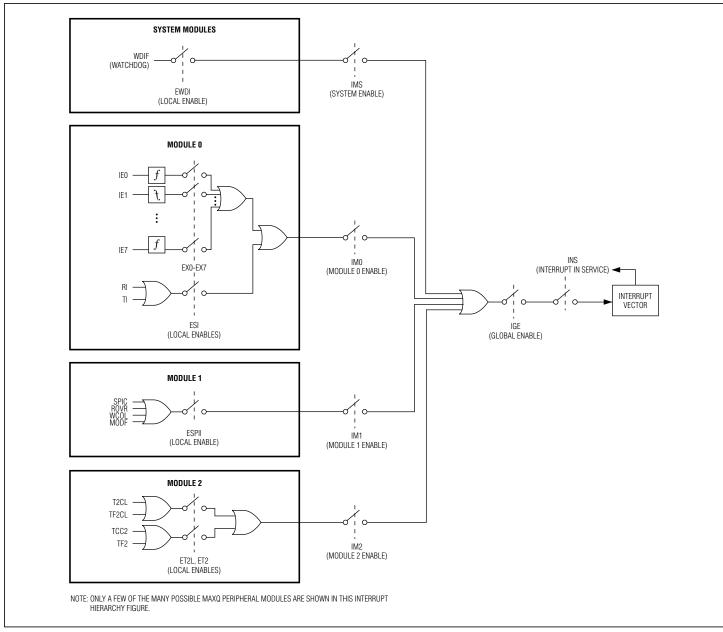

| Figure 1-13. MAXQ7665/MAXQ7666 Interrupt Source Hierarchy Example      | .1-25 |

|                                                                        |       |

# LIST OF TABLES

| Table 1-1. Register-to-Register Transfer Operations                            | .1-9  |

|--------------------------------------------------------------------------------|-------|

| Table 1-2. MAXQ7665/MAXQ7666 Register Modules                                  | .1-10 |

| Table 1-3. MAXQ7665A–MAXQ7665D Flash Memory Features                           | .1-12 |

| Table 1-4. MAXQ7666 Program Flash Features                                     | .1-12 |

| Table 1-5. MAXQ7666 Data Flash Features                                        | .1-13 |

| Table 1-6. MAXQ7665/MAXQ7666 Interrupt Sources and Control Bits                | .1-27 |

| Table 1-7. Accumulator Pointer Control Register Settings                       | .1-33 |

| Table 1-8. MAXQ7665/MAXQ7666 System Register Map    Map                        | .1-43 |

| Table 1-9. MAXQ7665/MAXQ7666 System Register Bit Functions and Reset Values    | .1-44 |

| Table 1-10. MAXQ7665/MAXQ7666 Peripheral Register Map    Map                   | .1-62 |

| Table 1-11. MAXQ7665/MAXQ7666 Module 0 Register Bit Functions and Reset Values | .1-63 |

| Table 1-12. MAXQ7665/MAXQ7666 Module 1 Register Bit Functions and Reset Values | .1-64 |

| Table 1-13. MAXQ7665/MAXQ7666 Module 2 Register Bit Functions and Reset Values | .1-65 |

| Table 1-14. MAXQ7665/MAXQ7666 Module 3 Register Bit Functions and Reset Values | .1-67 |

| Table 1-15. MAXQ7665/MAXQ7666 Module 4 Register Bit Functions and Reset Values | .1-68 |

| Table 1-16. MAXQ7665/MAXQ7666 Module 5 Register Bit Functions and Reset Values | .1-70 |

# SECTION 1: MAXQ7665/MAXQ7666 CORE ARCHITECTURE

## 1.1 Overview

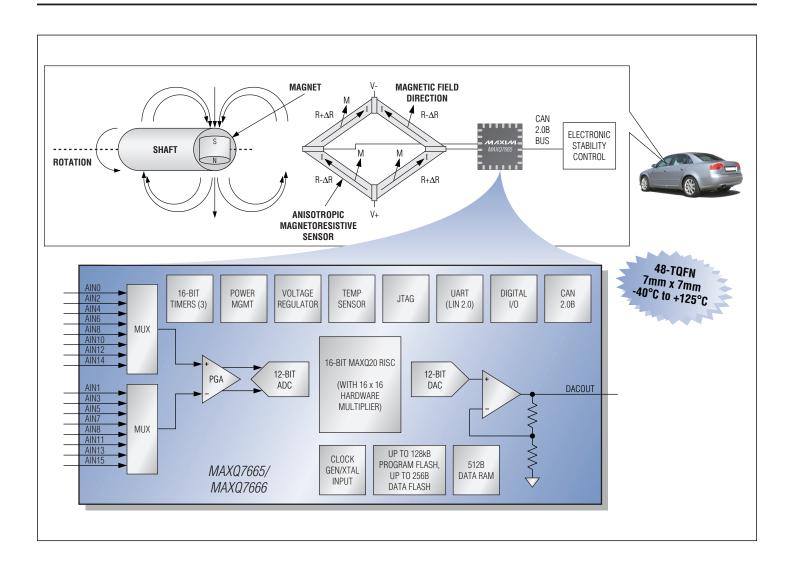

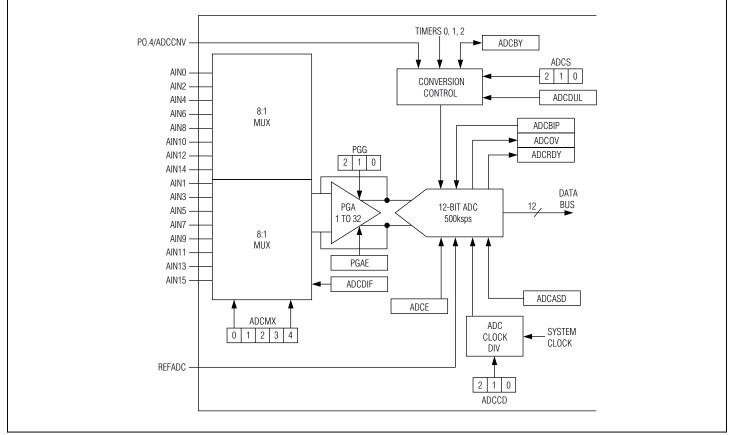

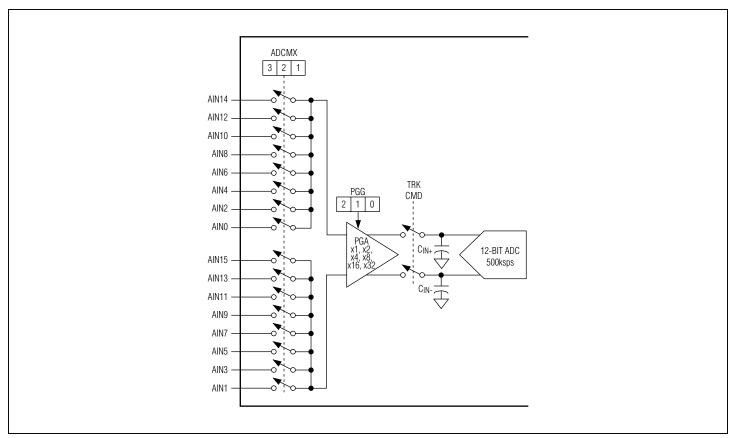

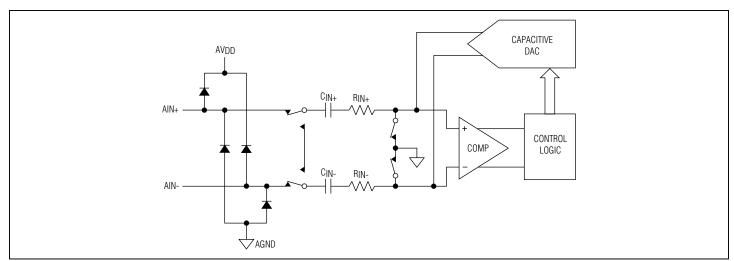

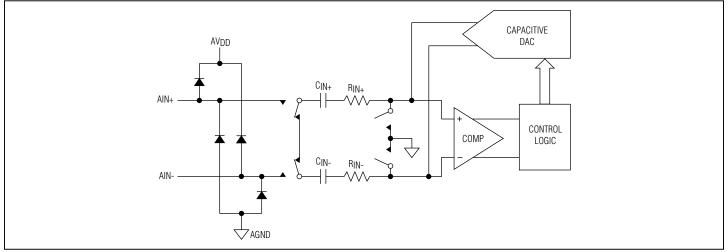

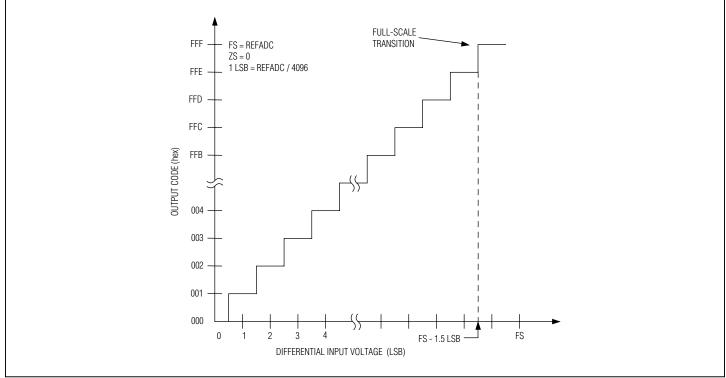

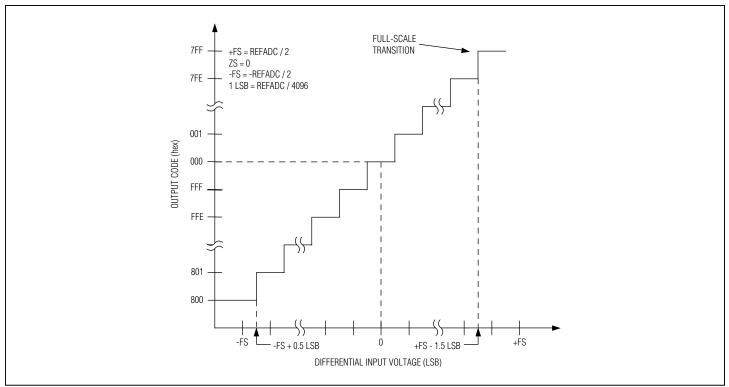

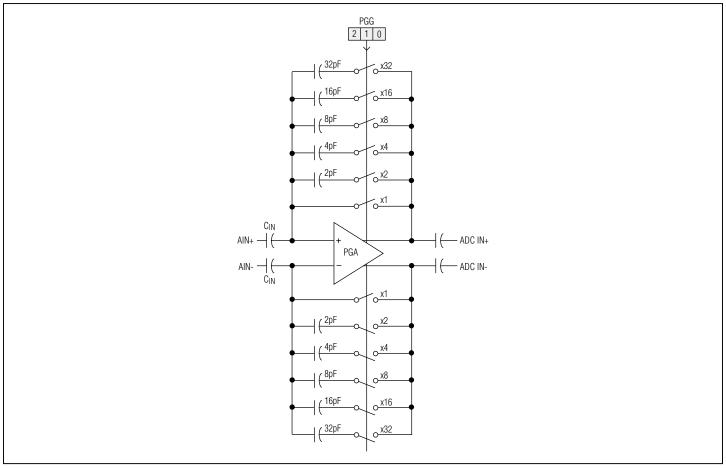

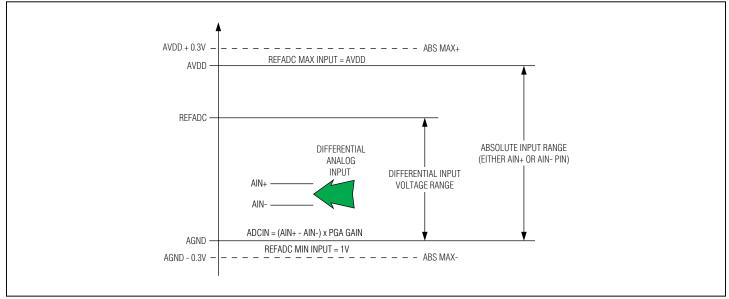

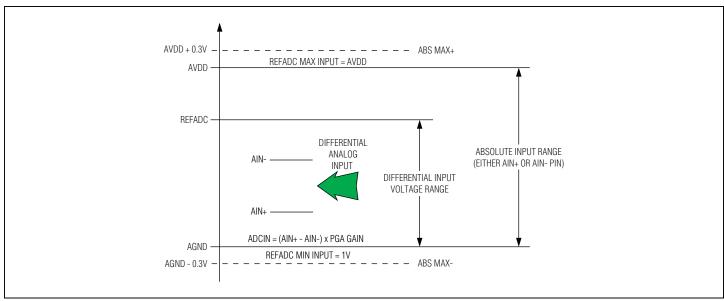

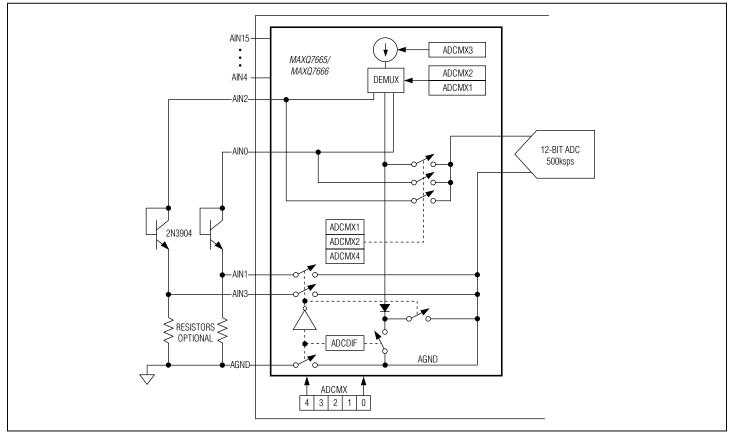

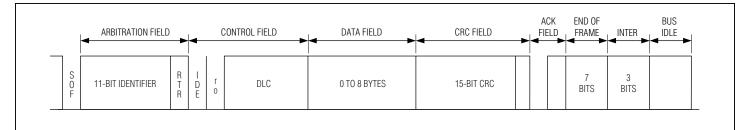

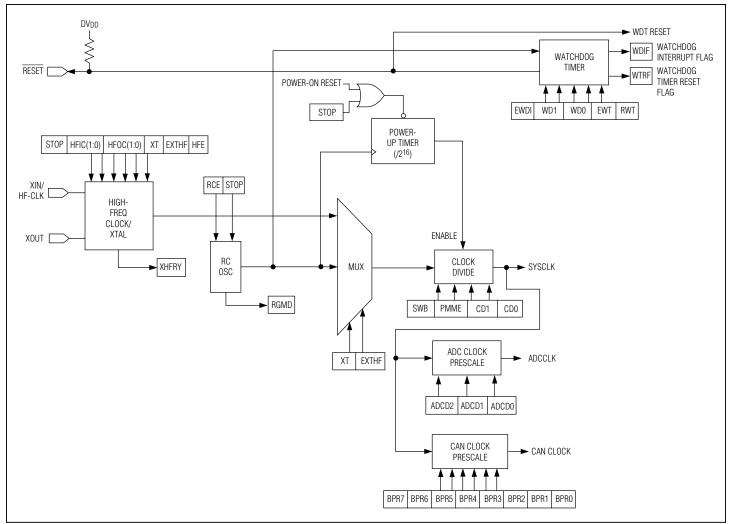

The MAXQ7665/MAXQ7666 are low-power, high-performance, 16-bit RISC microcontrollers based on the MAXQ® architecture. They include support for integrated, in-system-programmable flash memory and a wide range of peripherals including a 12-bit 500ksps SAR ADC with a programmable gain amplifier (PGA) and a full CAN 2.0B controller supporting transfer rates up to 1Mbps. The MAXQ7665/MAXQ7666 are ideally suited for low-cost, low-power embedded applications such as automotive, industrial controls, and building automation. Except where explicitly noted, the MAXQ7665 and MAXQ7666 features are identical.

The MAXQ7665/MAXQ7666 key features include:

- 8MHz, 16-bit, single-cycle RISC CPU with Harvard Memory Architecture

- Up to 64k x 16 (128kB) on-chip program flash (16kB program flash and dedicated 256B data flash in MAXQ7666) and 512 bytes internal RAM

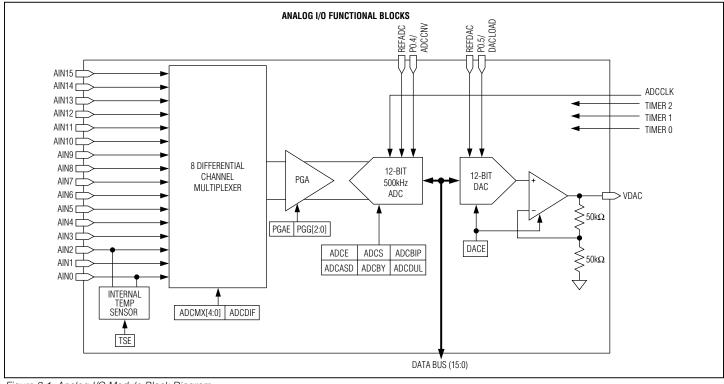

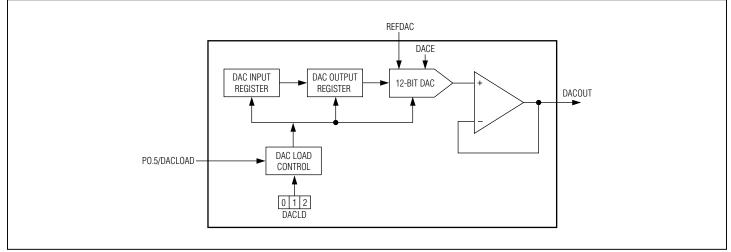

- High-precision, low-power analog input/output module including a 12-bit, 500ksps SAR ADC, 1x-32x PGA, 12-bit DAC and local/remote temperature sensor

- Full CAN 2.0B controller supporting transfer rates up to 1Mbps

- High-performance timer/digital I/O peripherals

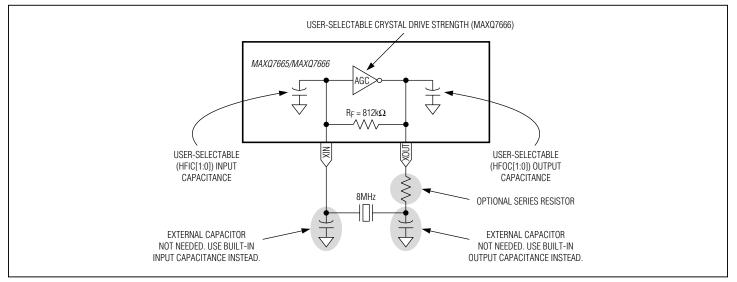

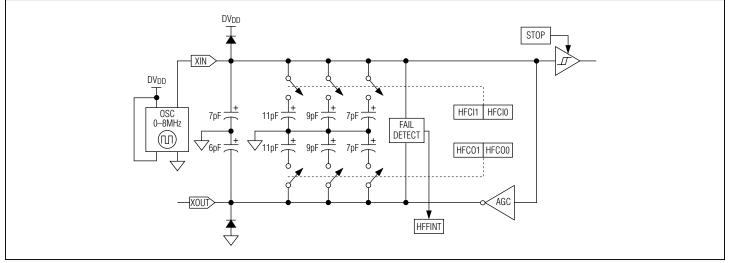

- Flexible crystal/clock module

- Advanced power monitoring/management module

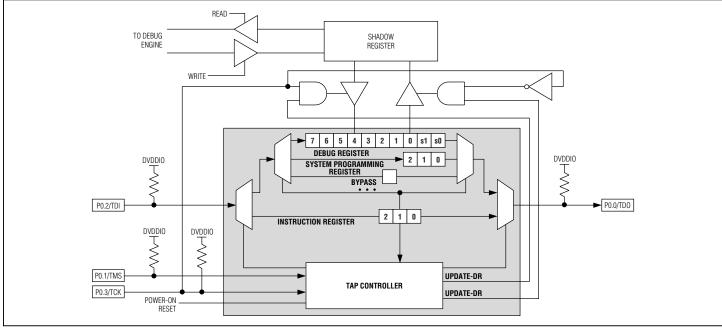

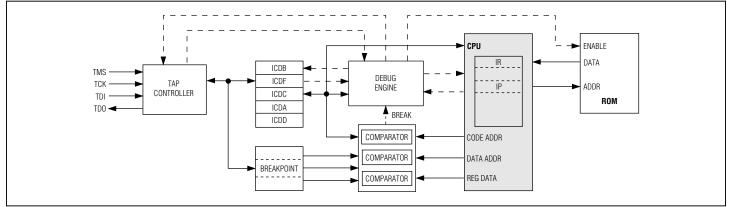

Figure 1-1. MAXQ7665/MAXQ7666 Block Diagram

## 1.1.1 References

The online MAXQ7665 and MAXQ7666 QuickView pages contain additional information and links to the data sheet. Errata sheets for the MAXQ products are available at <u>www.maxim-ic.com/errata</u>. For more information on other MAXQ microcontrollers, development hardware and software, frequently asked questions and software examples, visit the MAXQ home page at <u>www.maxim-ic.com/MAXQ</u>. For general questions and discussion of the MAXQ platform, visit our discussion board at <u>http://discuss.dalsemi.com</u>.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

### 1.1.2 Instruction Set

As part of the MAXQ family, the MAXQ7665/MAXQ7666 use the standard 16-bit MAXQ20 instruction set, with all instructions a fixed 16 bits in length. A register-based, transport-triggered architecture allows all instructions to be coded as simple transfer operations. All instructions reduce to either writing an immediate value to a destination register or memory location or moving data between registers and/or memory locations.

This simple top-level instruction decoding allows all instructions to be executed in a single cycle. Since all CPU operations are performed on registers only, any new functionality can be added by simply adding new register modules. The simple instruction set also provides maximum flexibility for code optimization by a compiler.

## 1.1.3 Harvard Memory Architecture

As part of the MAXQ family, the MAXQ7665/MAXQ7666 core architecture is based on the MAXQ20 design, which implements a 16-bit internal databus and ALU. Program memory, data memory, and register space on the MAXQ7665/MAXQ7666 follow the Harvard architecture model. Each type of memory is kept separate and is accessed by a separate bus, allowing different word lengths for different types of memory. Registers may be either 8 or 16 bits in width. Program memory is 16 bits in width to accommodate the standard MAXQ 16-bit instruction set. Data memory is also 16 bits in width but can be accessed in 8-bit or 16-bit modes for maximum flexibility.

The MAXQ7665/MAXQ7666 include a flexible memory management unit (MMU), which allows code to be executed from either the program flash, the utility ROM, or the internal data SRAM. Any of these three memory spaces may also be accessed in data space at any time, with the single restriction that whichever physical memory area is currently being used as program space cannot be read from in data space.

### 1.1.4 Register Space

Since all functions in the MAXQ family are accessed through registers, common functionality is provided through a common register set. Many of these registers provide the equivalent of higher level op codes by directly accessing the arithmetic logic unit (ALU), the loop counter registers, and the data pointer registers. Others, such as the interrupt registers, provide common control and configuration functions that are equivalent across all MAXQ microcontrollers.

The common register set, also known as the System Registers, includes the following:

- · ALU access and control registers, including working accumulator registers and the processor status flags

- Two Data Pointers and a Frame Pointer for data memory access

- Auto-decrementing Loop Counters for fast, compact looping

- · Instruction Pointer and other branching control access points

- Stack Pointer and an access point to the 16-bit-wide dedicated hardware stack

- Interrupt vector, identification, and masking registers

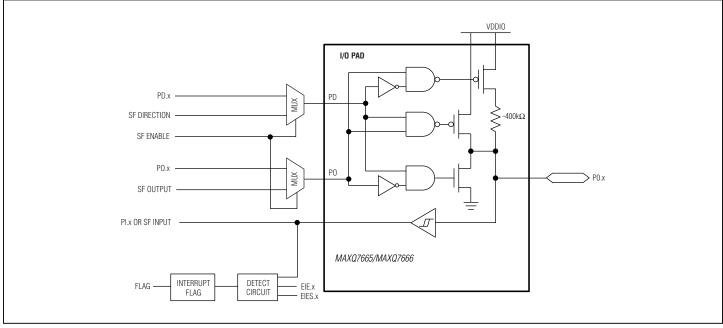

The MAXQ7665/MAXQ7666 peripheral register space (modules 0 to 5) contains registers that access the following peripherals:

- General-purpose, 8-bit, I/O port (P0)

- Serial UART interface

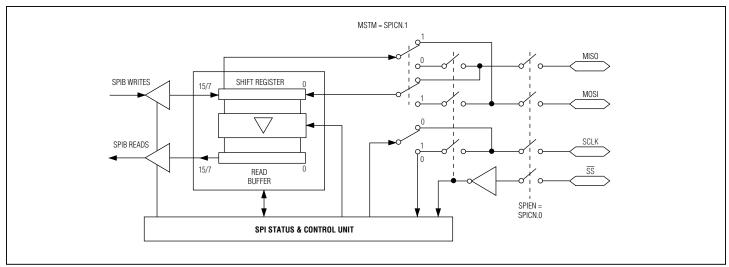

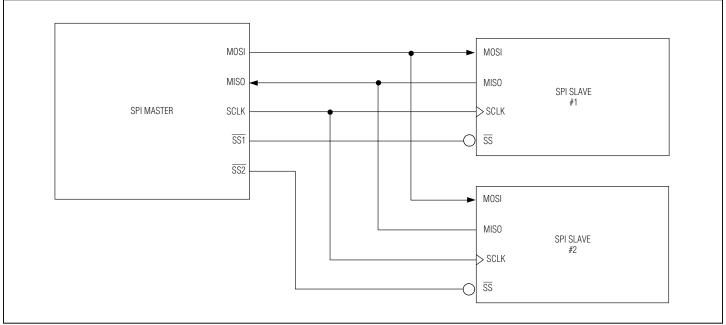

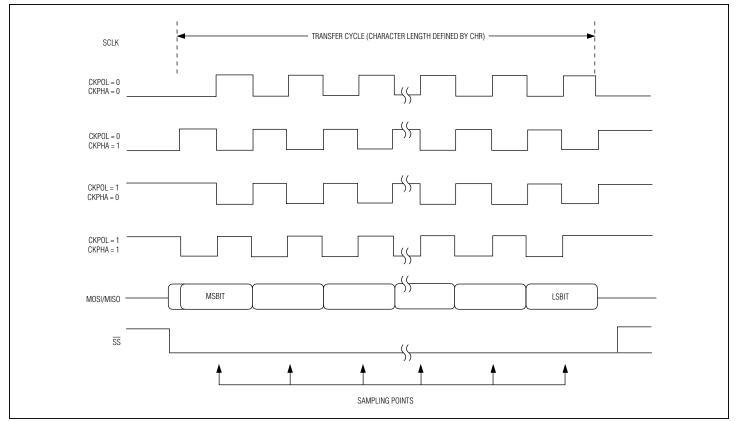

- Serial peripheral interface (SPI)

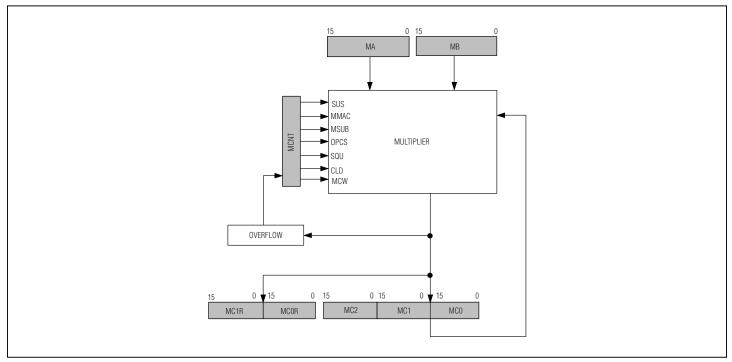

- Hardware multiplier

- JTAG debug engine

- Three programmable Type 2 timer/counters

- Controller area network (CAN) interface

- Analog input/output module

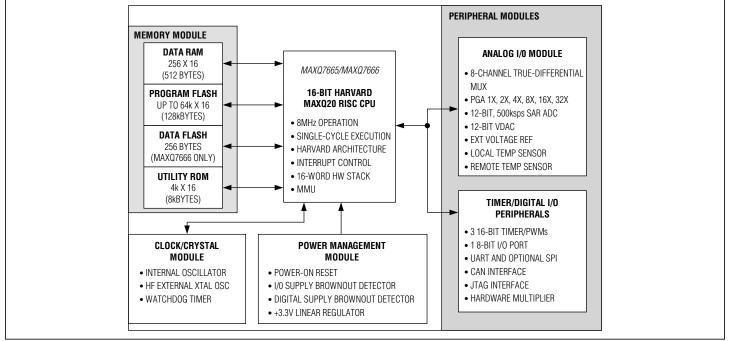

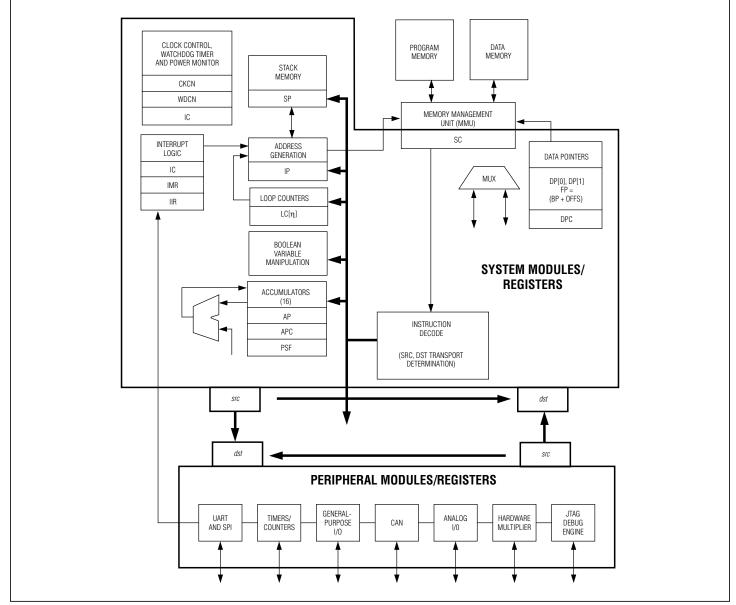

# **1.2 Architecture**

The MAXQ7665/MAXQ7666 architecture is designed to be modular and expandable. Top-level instruction decoding is extremely simple and based on transfers to and from registers. The registers are organized into functional modules, which are in turn divided into the system register and peripheral register groups. Figure 1-2 illustrates the modular architecture and the basic transport possibilities.

Figure 1-2. MAXQ7665/MAXQ7666 Transport-Triggered Architecture

Memory access from the MAXQ7665/MAXQ7666 is based on a Harvard architecture with separate address spaces for program and data memory. The simple instruction set and transport-triggered architecture allow the MAXQ7665/MAXQ7666 to run in a nonpipelined execution mode where each instruction can be fetched from memory, decoded, and executed in a single clock cycle. Data memory is accessed through one of three data pointer registers. Two of these data pointers, DP[0] and DP[1], are stand-alone 16-bit pointers. The third data pointer, FP, is composed of a 16-bit base pointer (BP) and an 8-bit offset register (OFFS). All three pointers support post-increment/decrement functionality for read operations and pre-increment/decrement for write operations. For the Frame Pointer (FP=BP[OFFS]), the increment/decrement operation is executed on the OFFS register and does not affect the base pointer (BP). Stack functionality is provided by dedicated memory with a 16-bit width and depth of 16. An on-chip memory management unit (MMU) is accessible through system registers to allow logical remapping of physical program and data spaces, and thus facilitates in-system programming and fast access to data tables, arrays, and constants physically located in program memory.

## **1.2.1 Instruction Decoding**

Every MAXQ7665/MAXQ7666 instruction is encoded as a single 16-bit word according to the format in Figure 1-3.

| FORMAT |   |   | DES | TINA | ΓΙΟΝ |   |   |   |   |   | SOU | RCE |   |   |   |

|--------|---|---|-----|------|------|---|---|---|---|---|-----|-----|---|---|---|

| f      | d | d | d   | d    | d    | d | d | S | S | S | S   | S   | S | S | S |

Figure 1-3. Instruction Word Format

Bit 15 (f) indicates the format for the source field of the instruction as follows:

- If f equals 0, the instruction is an immediate source instruction, and the source field represents an immediate 8-bit value.

- If f equals 1, the instruction is a register source instruction, and the source field represents the register that the source value will be read from.

Bits 0 to 7 (ssssssss) represent the source for the transfer. Depending on the value of the format field, this can either be an immediate value or a source register. If this field represents a register, the lower four bits contain the module specifier and the upper four bits contain the register index in that module.

Bits 8 to 14 (dddddd) represent the destination for the transfer. This value always represents a destination register, with the lower four bits containing the module specifier and the upper three bits containing the register subindex within that module.

Since the source field is 8 bits wide and 4 bits are required to specify the module, any one of 16 registers in that module may be specified as a source. However, the destination field has one less bit, which means that only eight registers in a module can be specified as a destination in a single-cycle instruction.

While the asymmetry between source and destination fields of the op code may initially be considered a limitation, this space can be used effectively. Firstly, since read-only registers will never be specified as destinations, they can be placed in the second eight locations in a module to give single-cycle read access. Secondly, there are often critical control or configuration bits associated with system and certain peripheral modules where limited write access is beneficial (e.g., watchdog-timer enable and reset bits). By placing such bits in one of the upper 24 registers of a module, this write protection is added in a way that is virtually transparent to the assembly source code. Anytime that it is necessary to directly select one of the upper 24 registers as a destination, the prefix register PFX is used to supply the extra destination bits. This prefix register write is inserted automatically by the assembler and requires one additional execution cycle.

The MAXQ7665/MAXQ7666 architecture is transport-triggered. This means that writing to or reading from certain register locations will also cause side effects to occur. These side effects form the basis for the higher level op codes defined by the assembler, such as ADDC, OR, JUMP, and so on. While these op codes are actually implemented as MOVE instructions between certain register locations, the encoding is handled by the assembler and need not be a concern to the programmer. The registers defined in the System Register and Peripheral Register maps operate as described in the documentation; the unused "empty" locations are the ones used for these special cases.

The MAXQ7665/MAXQ7666 instruction set is designed to be highly orthogonal. All arithmetic and logical operations that use two registers can use any register along with the accumulator. Data can be transferred between any two registers in a single instruction.

### 1.2.2 Register Space

The MAXQ7665/MAXQ7666 architecture provides a total of 16 register modules. Each of these modules contains 32 registers. Of these possible 16 register modules, only 13 are used on the MAXQ7665/MAXQ7666—seven for system registers and six for peripheral registers. The first eight registers in each module may be read from or written to in a single cycle; the second eight registers may be read from in a single cycle and written to in two cycles (by using the prefix register PFX); the last 16 registers may be read or written in two cycles (always requiring use of the prefix register PFX).

Registers may be either 8 or 16 bits in length. Within a register, any number of bits can be implemented; bits not implemented are fixed at zero. Data transfers between registers of different sizes are handled as shown in Table 1-1.

- If the source and destination registers are both 8 bits wide, data is transferred bit to bit accordingly.

- If the source register is 8 bits wide and the destination register is 16 bits wide, the data from the source register is transferred into the lower 8 bits of the destination register. The upper 8 bits of the destination register are set to the current value of the prefix register; this value is normally zero, but it can be set to a different value by the previous instruction if needed. The prefix register reverts back to zero after one cycle, so this must be done by the instruction immediately before the one that will be using the value.

- If the source register is 16 bits wide and the destination register is 8 bits wide, the lower 8 bits of the source are transferred to the destination register.

- If both registers are 16 bits wide, data is copied bit to bit.

## Table 1-1. Register-to-Register Transfer Operations

| SOURCE REGISTER SIZE | DESTINATION REGISTER | PREFIX SET?  | DESTINATION   | SET TO VALUE |

|----------------------|----------------------|--------------|---------------|--------------|

| (BITS)               | SIZE (BITS)          | FREFIX SET : | HIGH 8 BITS   | LOW 8 BITS   |

| 8                    | 8                    | —            |               | Source [7:0] |

| 8                    | 16                   | No           | 00h           | Source [7:0] |

| 8                    | 16                   | Yes          | Prefix [7:0]  | Source [7:0] |

| 16                   | 8                    |              |               | Source [7:0] |

| 16                   | 16                   | No           | Source [15:8] | Source [7:0] |

The above rules apply to all data movements between defined registers. Data transfer to/from undefined register locations has the following behavior:

- If the destination is an undefined register, the MOVE is a dummy operation but may trigger an underlying operation according to the source register (e.g., @DP[n]--).

- If the destination is a defined register and the source is undefined, the source data for the transfer will depend upon the source module width. If the source is from a module containing 8-bit or 8-bit and 16-bit source registers, the source data will be equal to the prefix data concatenated with 00h. If the source is from a module containing only 16-bit source registers, 0000h source data is used for the transfer.

The 16 available register modules are broken up into two different groups. The low six modules (specifiers 0h through 5h) are known as the Peripheral Register modules, while the high 10 modules (specifiers 6h to Fh) are known as the System Register modules. These groupings are descriptive only, as there is no difference between accessing the two register groups from a programming perspective.

The System Registers define basic functionality that remains the same across all products based on the MAXQ20 architecture. This includes all register locations that are used to implement higher level op codes as well as the following common system features.

- ALU (MAXQ20: 16 bits) and associated status flags (zero, equals, carry, sign, overflow)

- 16 working accumulator registers (MAXQ20: 16-bit width), along with associated control registers

- Instruction pointer

- Registers for interrupt control, handling, and identification

- Auto-decrementing loop counters for fast, compact looping

- Two data pointer registers and a frame pointer for data memory access

The MAXQ7665/MAXQ7666 peripheral register space (modules 0 to 5) contains registers that access the following peripherals:

- General-purpose, 8-bit, I/O port (P0)

- External interrupts (up to 8)

- Three programmable Type 2 timer/counters

- Serial UART interface

- SPI

- CAN interface

- Analog input/output module

- Hardware multiplier

- JTAG debug engine

The lower 8 bits of all registers in modules 0 to 5 (as well as the AP module M8) are bit addressable.

## Table 1-2. MAXQ7665/MAXQ7666 Register Modules

| REGISTER |       | MODULE NAME (BASE SPECIFIER) |        |        |       |      |      |       |        |     |     |      |     |

|----------|-------|------------------------------|--------|--------|-------|------|------|-------|--------|-----|-----|------|-----|

| INDEX    | МО    | M1                           | M2     | М3     | M4    | M5   | M8   | M9    | M11    | M12 | M13 | M14  | M15 |

| 00h      | PO0   | MCNT                         | T2CNA0 | T2CNA2 | COC   | VMC  | AP   | A[0]  | PFX[0] | IP  |     |      |     |

| 01h      |       | MA                           | T2H0   | T2H2   | COS   | APE  | APC  | A[1]  | PFX[1] |     | SP  |      |     |

| 02h      |       | MB                           | T2RH0  | T2RH2  | COIR  | ACNT |      | A[2]  | PFX[2] |     | IV  |      |     |

| 03h      | EIFO  | MC2                          | T2CH0  | T2CH2  | COTE  | DCNT |      | A[3]  | PFX[3] |     |     | OFFS | DP0 |

| 04h      |       | MC1                          | T2CNA1 |        | CORE  | DACI | PSF  | A[4]  | PFX[4] |     |     | DPC  |     |

| 05h      |       | MC0                          | T2H1   |        | COR   |      | IC   | A[5]  | PFX[5] |     |     | GR   |     |

| 06h      |       | SPIB                         | T2RH1  |        | CODP  | DACO | IMR  | A[6]  | PFX[6] |     | LC0 | GRL  |     |

| 07h      | SBUF0 | SPICN                        | T2CH1  |        | CODB  |      |      | A[7]  | PFX[7] |     | LC1 | BP   | DP1 |

| 08h      | PIO   | SPICF                        | T2CNB0 | T2CNB2 | CORMS | ADCD | SC   | A[8]  |        |     |     | GRS  |     |

| 09h      |       | SPICK                        | T2V0   | T2V2   | COTMA | TSO  |      | A[9]  |        |     |     | GRH  |     |

| 0Ah      |       | FCNTL                        | T2R0   | T2R2   |       | AIE  |      | A[10] |        |     |     | GRXL |     |

| 0Bh      | EIE0  | FDATA                        | T2C0   | T2C2   |       | ASR  | IIR  | A[11] |        |     |     | FP   |     |

| 0Ch      |       | MC1R                         | T2CNB1 |        |       | OSCC |      | A[12] |        |     |     |      |     |

| 0Dh      |       | MCOR                         | T2V1   |        |       |      |      | A[13] |        |     |     |      |     |

| 0Eh      |       |                              | T2R1   |        |       |      | CKCN | A[14] |        |     |     |      |     |

| 0Fh      |       |                              | T2C1   |        |       |      | WDCN | A[15] |        |     |     |      |     |

| 10h      | PD0   |                              | T2CFG0 | T2CFG2 |       |      |      |       |        |     |     |      |     |

| 11h      |       |                              | T2CFG1 |        | C0M1C |      |      |       |        |     |     |      |     |

| 12h      |       |                              |        |        | C0M2C |      |      |       |        |     |     |      |     |

| 13h      | EIES0 |                              |        |        | C0M3C |      |      |       |        |     |     |      |     |

| 14h      |       |                              |        |        | C0M4C |      |      |       |        |     |     |      |     |

| 15h      |       |                              |        |        | C0M5C |      |      |       |        |     |     |      |     |

| 16h      |       |                              |        |        | COM6C |      |      |       |        |     |     |      |     |

| REGISTER |                          |                        |       |    | мс                | DULE NA                | ME (BASE | SPECIFIE | R)         |     |                    |                    |     |

|----------|--------------------------|------------------------|-------|----|-------------------|------------------------|----------|----------|------------|-----|--------------------|--------------------|-----|

| INDEX    | МО                       | M1                     | M2    | МЗ | M4                | M5                     | M8       | M9       | M11        | M12 | M13                | M14                | M15 |

| 17h      |                          |                        |       |    | C0M7C             |                        |          |          |            |     |                    |                    |     |

| 18h      |                          |                        | ICDT0 |    | C0M8C             |                        |          |          |            |     |                    |                    |     |

| 19h      |                          |                        | ICDT1 |    | C0M9C             |                        |          |          |            |     |                    |                    |     |

| 1Ah      |                          |                        | ICDC  |    | C0M10C            |                        |          |          |            |     |                    |                    |     |

| 1Bh      |                          |                        | ICDF  |    | C0M11C            |                        |          |          |            |     |                    |                    |     |

| 1Ch      |                          | FADDR                  | ICDB  |    | C0M12C            |                        |          |          |            |     |                    |                    |     |

| 1Dh      | SCON0                    |                        | ICDA  |    | C0M13C            |                        |          |          |            |     |                    |                    |     |

| 1Eh      | SMD0                     |                        | ICDD  |    | C0M14C            |                        |          |          |            |     |                    |                    |     |

| 1Fh      | PR0                      |                        |       |    | C0M15C            |                        |          |          |            |     |                    |                    |     |

|          | RESERVED<br>OR<br>OPCODE | PORT<br>PINS<br>(GPIO) | ANE   |    | TERRUPT<br>DNTROL | HARDWARE<br>MULTIPLIER | TIMERS   | CAN      | ANAL<br>VO |     | C ARRAY,<br>DNTROL | OTHER<br>FUNCTIONS | ]   |

# Table 1-2. MAXQ7665/MAXQ7666 Register Modules (continued)

## 1.2.3 Memory Organization

Beyond the internal register space, memory on the MAXQ7665/MAXQ7666 microcontrollers is organized according to a Harvard architecture, with a separate address space and bus for program memory and data memory. Stack memory is also separate and is accessed through a dedicated register set.

To provide additional memory map flexibility, an MMU allows data memory space to be mapped into a predefined program memory segment, thus affording the possibility of code execution from data memory. Additionally, program memory space can be made accessible as data space, allowing access to constant data stored in program memory. All memory is internal, and physical memory segments (other than the stack and register memories) can be accessed as either program memory or as data memory, but not both at once.

### 1.2.3.1 Program Memory

The MAXQ7665/MAXQ7666 contain up to 64k x 16 (128kB) of flash memory, which normally serves as program memory. When executing from the data SRAM or utility ROM, this memory is mapped to data space and can be used for lookup tables and similar functions. Flash memory mapped into data space can be read from directly, like any other type of data memory. However, writing to flash memory must be done by calling the in-application functions provided by the utility ROM. The utility ROM provides routines to carry out the necessary operations (erase, write) on flash memory.

Table 1-3 summarizes the features of the flash memory supported in the MAXQ7665A–MAXQ7665D devices. The MAXQ7666 device features a 256B data flash in addition to 16kB program flash. The MAXQ7666 flash is different from the MAXQ7665A–MAXQ7665D and its features are summarized in Tables 1-4 and 1-5. Refer to the respective data sheets for additional information.

Program memory begins at address 0000h and is contiguous through the internal program memory. The actual size of the on-chip program memory available for user application is product dependent. Given a 16-bit program address bus, the maximum program space is 64kWords. Since the codewords are 16 bits, the program memory is, therefore, a 64k x 16 linear space.

# Table 1-3. MAXQ7665A–MAXQ7665D Flash Memory Features

| FEATURE                   | MAXQ7665A                 | MAXQ7665B                         | MAXQ7665C                          | MAXQ7665D                |

|---------------------------|---------------------------|-----------------------------------|------------------------------------|--------------------------|

| Flash Type                | Туре А                    | Туре А                            | Туре А                             | Туре А                   |

| Flash Size                | 128kB (64k x 16)          | 64kB (32k x 16)                   | 48kB (24k x 16)                    | 32kB (16k x 16)          |

| Flash Organization        | 5 Sectors                 | 4 Sectors                         | 3 Sectors                          | 3 Sectors                |

| Sector Address/Size       | 0000h–7FFFh<br>(32k x 16) | 0000h–3FFFh<br>(16k x 16)         | 0000h–3FFFh<br>(16k x 16)          | 0000h–1FFFh<br>(8k x 16) |

|                           | 8000h–BFFFh<br>(16k x 16) | 4000h–5FFFh<br>(8k x 16)          | 4000h–4FFFh<br>(4k x 16)           | 2000h–2FFFh<br>(4k x 16) |

|                           | C000h–DFFFh<br>(8k x 16)  | 6000h–6FFFh<br>(4k x 16)          | 5000h–5FFFh<br>(4k x 16)           | 3000h–3FFFh<br>(4k x 16) |

|                           | E000h–EFFFh<br>(4k x 16)  | 7000h–7FFFh<br>(4k x 16)          | _                                  | _                        |

|                           | F000h–FFFFh<br>(4k x 16)  | _                                 | _                                  | _                        |

| Flash Erase               | Erase All                 | Erase All                         | Erase All                          | Erase All                |

| TIASTI LIASE              | Sector Erase              | Sector Erase                      | Sector Erase                       | Sector Erase             |

| Flash Program             | Word Write                | Word Write                        | Word Write                         | Word Write               |

| n Application Programming | Ye                        | es, using utility ROM routines. S | ee Section 15 for more information | on.                      |

| In System Programming     | Yes, using                | g utility ROM JTAG bootstrap lo   | ader. See Section 12 for more in   | formation.               |

# Table 1-4. MAXQ7666 Program Flash Features

| FEATURE                    | MAXQ7666                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Flash Type                 | Туре F                                                                             |

| Program Flash Size         | 16kB (8k x 16)                                                                     |

| Brogrom Fleph Organization | 256 Pages                                                                          |

| Program Flash Organization | 1 Page = 64B (32 x 16)                                                             |

|                            | 0000h-001Fh (Page 0)                                                               |

|                            | 0020h-003Fh (Page 1)                                                               |

|                            | 0040h-005Fh (Page 2)                                                               |

| Program Flash Page Address |                                                                                    |

|                            | 1FC0h–1FDFh (Page 254)                                                             |

|                            | 1FE0h–1FFFh (Page 255)                                                             |

|                            | Erase All                                                                          |

| Program Flash Erase        | 2 Page Erase                                                                       |

| Program Flash Write        | 1 Page Write                                                                       |

| In Application Programming | Yes, using utility ROM routines. See Section 16 for more information.              |

| In System Programming      | Yes, using utility ROM JTAG bootstrap loader. See Section 12 for more information. |

## Table 1-5. MAXQ7666 Data Flash Features

| FEATURE                                | MAXQ7666                                                              |

|----------------------------------------|-----------------------------------------------------------------------|

| Flash Type                             | Туре F                                                                |

| Data Flash Size                        | 256B (128 x 16)                                                       |

| Data Flash Organization (Regular Mode) | 128 Pages                                                             |

| Data Flash Organization (negular Mode) | 1 Page = 2B (1 x 16)                                                  |

|                                        | 4000h (Page 0)                                                        |

|                                        | 4001h (Page 1)                                                        |

| Data Flash Page Address (Regular Mode) | 4002h (Page 2)                                                        |

| _                                      | 407Fh (Page 127)                                                      |

| Data Flash Erase                       | Erase All                                                             |

| (Regular Mode)                         | 2 Page Erase                                                          |

| Data Flash Write<br>(Regular Mode)     | 1 Page Write                                                          |

| Data Flash Organization<br>(Even Mode) | 64 Even Pages                                                         |

|                                        | 1 Page = 2B (1 x 16)                                                  |

|                                        | 4000h (Page 0)                                                        |

|                                        | 4002h (Page 1)                                                        |

| Data Flash Page Address (Even Mode)    | 4004h (Page 2)                                                        |

|                                        |                                                                       |

|                                        | 407Eh (Page 63)                                                       |

| Data Flash Erase                       | Erase All                                                             |

| (Even Mode)                            | 1 Page Erase                                                          |

| Data Flash Write<br>(Even Mode)        | 1 Page Write                                                          |

| In Application Programming             | Yes, using utility ROM routines. See Section 16 for more information. |

| In System Programming                  | Not supported, only in application programming.                       |

Program memory is accessed directly by the program fetching unit and is addressed by the Instruction Pointer register. From an implementation perspective, system interrupts and branching instructions simply change the contents of the Instruction Pointer and force the op code fetch from a new program location. The Instruction Pointer is direct read/write accessible by the user software; write access to the Instruction Pointer will force program flow to the new address on the next cycle following the write. The contents of the Instruction Pointer will be incremented by 1 automatically after each fetch operation. The Instruction Pointer defaults to 8000h, which is the starting address of the utility ROM. The default IP setting of 8000h is assigned to allow initial in-system programming to be accomplished with utility ROM code assistance. The utility ROM code interrogates a specific register bit in order to decide whether to execute in-system programming or jump immediately to user code starting at 0000h. The user code reset vector should always be stored in the lowest bytes of the program memory.

### 1.2.3.2 Utility ROM

A utility ROM (4k x 16) is placed in the upper 32kWord program memory space starting at address 8000h. This utility ROM provides the following system utility functions:

- Reset vector

- Bootstrap function for system initialization

- In-application programming

- In-circuit debug

Following each reset, the processor automatically starts execution at address 8000h in the utility ROM, allowing ROM code to perform any necessary system support functions. Next, the System Programming Enable (SPE) bit is examined to determine whether system programming should commence or whether that code should be bypassed, instead forcing execution to vector to the start of user program code. When the SPE bit is set to logic 1, the processor will execute the prescribed Bootstrap Loader mode program that resides in utility ROM. The SPE bit defaults to 0. To enter the Bootstrap Loader mode, the SPE bit can be set to 1 during reset via the JTAG interface. When in-system programming is complete, the Bootstrap Loader can clear the SPE bit and reset the device such that the insystem programming routine is subsequently bypassed.

The MAXQ7665/MAXQ7666 application programming routines available as part of the utility ROM are covered in Sections 15 and 16. The MAXQ7665/MAXQ7666 JTAG test access port, in-circuit debug, and bootstrap loader mode for in-system programming are covered in Sections 10, 11, and 12.

### 1.2.3.3 Data Memory

The MAXQ7665/MAXQ7666 contain 256 x 16 (512 bytes) of on-chip data SRAM that can be mapped into either program or data space. The contents of this SRAM are indeterminate after power-on reset, but are maintained during stop mode and across non-POR resets, as long as the DVDD supply stays within the acceptable range.

On-chip data memory begins at address 0000h and is contiguous through the internal data memory. Data memory is accessed via indirect register addressing through a Data Pointer (@DP[n]) or Frame Pointer (@BP[OFFS]). The Data Pointer is used as one of the operands in a MOVE instruction. If the Data Pointer is used as source, the core performs a Load operation that reads data from the data memory location addressed by the Data Pointer. If the Data Pointer is used as destination, the core executes a Store operation that writes data to the data memory location addressed by the Data Pointer. The Data Pointer. The Data Pointer can be directly accessed by the user software.

The core incorporates two 16-bit Data Pointers (DP[0] and DP[1]) to support data memory accessing. All Data Pointers support indirect addressing mode and indirect addressing with auto-increment or auto-decrement. Data Pointers DP[0] and DP[1] can be used as post increment/decrement source pointers by a MOVE instruction or pre increment/decrement destination pointers by a MOVE instruction. Using Data Pointer indirectly with "++" will automatically increase the content of the active Data Pointer by 1 immediately following the execution of read data transfer (@DP[n]++) or immediately preceding the execution of a write operation (@++DP[n]). Using Data Pointer indirectly with "---" will decrease the content of the active Data Pointer by 1 immediately following the execution of read data transfer (@DP[n]--) or immediately preceding the execution of a write operation (@--DP[n]).

The Frame Pointer (BP[OFFS]) is formed by 16-bit unsigned addition of Frame Pointer Base Register (BP) and Frame Pointer Offset Register (OFFS). Frame Pointer can be used as a post increment/decrement source pointer by a MOVE instruction or as a pre increment/decrement destination pointer. Using Frame Pointer indirectly with "++" (@BP[++OFFS] for a write or @BP[OFFS++] for a read) will automatically increase the content of the Frame Pointer Offset by 1 immediately before or after the execution of data transfer depending upon whether it is used as a destination or source pointer respectively. Using Frame Pointer indirectly with "--" (@BP[--OFFS] for a write or @BP[OFFS--] for a read) will decrease the content of the Frame Pointer Offset by 1 immediately before/after execution of data transfer depending upon whether it is used as a destination or source pointer respectively. Note that the increment/decrement function affects the content of the OFFS register only, while the contents of the BP register remain unaffected by the borrow/carry out from the OFFS register.

A data memory cycle contains only one system clock period to support fast internal execution. This allows read or write operations on SRAM to be completed in one clock cycle. Data memory mapping and access control are handled by the MMU. Read/write access to the data memory can be in word or in byte.

When using the in-circuit debugging features of the MAXQ7665/MAXQ7666, the top 19 bytes (bytes 0x1ED to 0x1FF) of the SRAM must be reserved for saved state storage and working space for the debugging routines in the utility ROM. If in-circuit debug will not be used, the entire SRAM is available for application use.

### 1.2.3.4 Stack Memory

The MAXQ7665/MAXQ7666 provide a 16 x 16 hardware stack to support subroutine calls and system interrupts. A 16-bit wide on-chip stack is provided by the MAXQ7665/MAXQ7666 for storage of program return addresses and general-purpose use. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and when an interrupt is serviced; it can also be used explicitly to store and retrieve data by using the @SP- - source, @++SP destination, or the PUSH, POP, and POPI instructions. The POPI instruction acts identically to the POP instruction except that it additionally clears the INS bit.

The width of the stack is 16 bits to accommodate the instruction pointer size. The stack depth is 16 for the MAXQ7665/MAXQ7666. As the stack pointer register SP is used to hold the index of the top of the stack, the maximum size of the stack allowed is defined by the number of bits defined in the SP register (e.g., 4 bits for stack depth of 16).

On reset, the stack pointer SP initializes to the top of the stack (e.g. 0Fh for a 16-word stack). The CALL, PUSH, and interrupt vectoring operations increment SP and then store a value at @SP. The RET, RETI, POP, and POPI operations retrieve the value at @SP and then decrement SP.

As with the other RAM-based modules, the stack memory is initialized to indeterminate values upon reset or power-up. Stack memory is dedicated for stack operations only and cannot be accessed through program or data address spaces.

When using the in-circuit debugging features of the MAXQ7665/MAXQ7666, one word of the stack must be reserved to store the return location when execution branches into the debugging routines in the utility ROM. If in-circuit debug will not be used, the entire stack is available for application use.

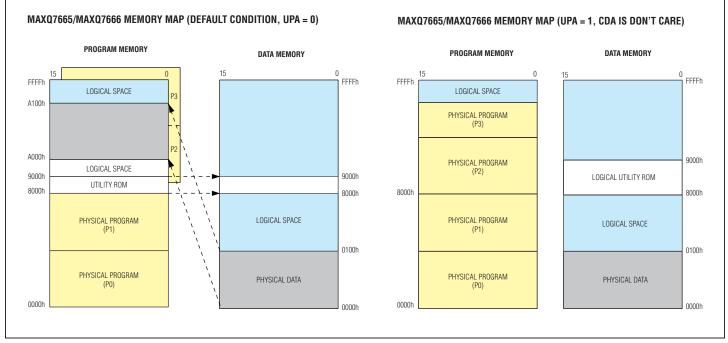

### 1.2.3.5 Pseudo-Von Neumann Memory Mapping

The MAXQ7665/MAXQ7666 support a pseudo-Von Neumann memory structure that can merge program and data into a linear memory map. This is accomplished by mapping the data memory into the program space or mapping program memory segment into the data space. Program memory from 0000h to 7FFFh is the normal user code segment, followed by the utility ROM segment. The uppermost part of the 64kWord memory is the logical area for data memory when accessed as a code segment.

The program memory is logically divided into four program pages:

- P0 contains the lower 16kWords,

- P1 contains the second 16kWords,

- P2 contains the third 16kWords, and

- P3 contains the fourth 16kWords.

By default, P2 and P3 are not accessible for program execution until they are explicitly activated by the user software. The Upper Program Access (UPA) bit must be set to logic 1 to activate P2 and P3. Once UPA is set, P2 and P3 will occupy the upper half of the 64kWord program space. In this configuration (UPA = 1), the utility ROM cannot be accessed as program memory and the physical data memory cannot be accessed logically in program space.

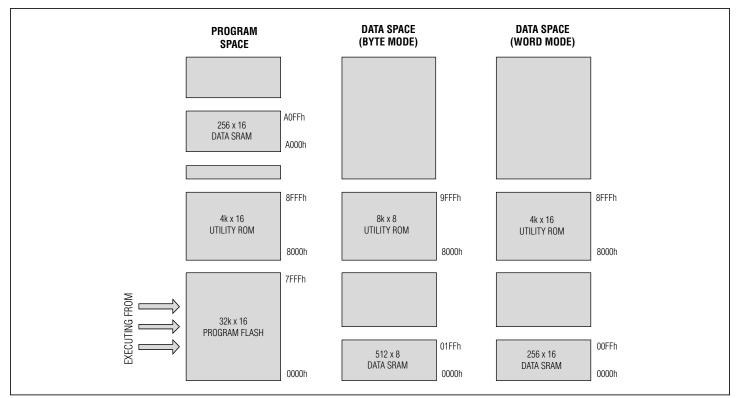

The logical mapping of physical program memory page(s) into data space depends upon two factors: physical memory currently in use for program execution; and word/byte data memory access selection. If execution is from the utility ROM, physical program memory page(s) can logically be mapped to the upper half of data memory space. If logical data memory is used for execution, physical program memory page(s) can logically be mapped to the lower half of data memory space. If byte access mode is selected, only one page (16kWords) may be logically mapped, as just defined, to either the upper or lower half of data memory overlapping in the byte access mode is selected, two pages (32kWords total) may be logically mapped to data memory. To avoid memory overlapping in the byte access mode, the physical data memory should be confined to the address range 0000h to 3FFFh in word mode. The selection of physical memory page or pages to be logically mapped to data space is determined by the Code Access Bits (CDA1:0):

| CDA1:0 | SELECTED PAGE IN BYTE MODE | SELECTED PAGE IN<br>WORD MODE |

|--------|----------------------------|-------------------------------|

| 00     | PO                         | P0 and P1                     |

| 01     | P1                         | P0 and P1                     |

| 10     | P2                         | P2 and P3                     |

| 11     | P3                         | P2 and P3                     |

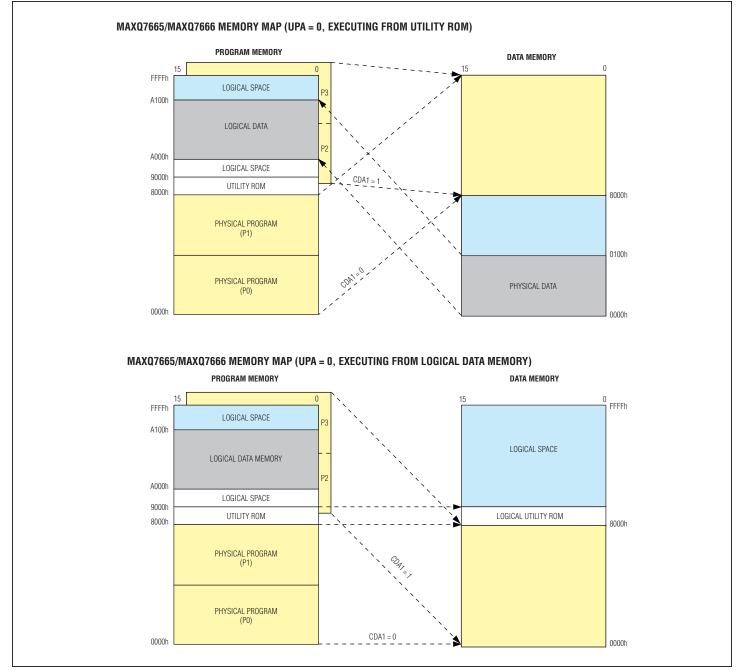

Figure 1-4 summarizes the default memory maps for this memory structure. The primary difference lies in the reset default settings for the data pointer Word/Byte Mode Select (WBSn) bits. The WBSn bits of the MAXQ7665/MAXQ7666 default to word access mode (WBSn = 1).

Figure 1-4. Pseudo-Von Neumann Memory Map (MAXQ7665/MAXQ7666 Default)

### 1.2.3.6 Pseudo-Von Neumann Memory Access

The pseudo-Von Neumann memory mapping is straightforward if there is no memory overlapping among the program, utility ROM, and data memory segments. However, for applications requiring large-size program memory, the paging scheme can be used to selectively activate those overlapped memory segments. The UPA bit can be used to activate the upper half of the physical program code (P2 and P3) for program execution. When accessing the program memory as data, the CDA bits can be used to select one of the four program pages as needed. Full data memory access to any of the four physical program memory pages is based on the assumption that the maximum physical data memory is in the range of 16k x 16. The other restriction for accessing the pseudo-Von Neumann map is that when program execution is in a particular memory segment, the same memory segment cannot be simultaneously be accessed as data.

When executing from the lower 32k program space (P0 and P1):

- The upper half of the code segment (P2 and P3) is accessible as program if the UPA bit is set to 1.

- The physical data memory is available for accessing as a code segment with offset at A000h if the UPA bit is 0.

- Load and Store operations addressed to physical data memory are executed as normal.

- The utility ROM can be read as data, starting at 8000h of the data space.

When executing from the utility ROM (only allowable when UPA = 0):

- The lower 32k program space (P0 and P1) functions as normal program memory.

- The upper half of the code segment (P2 and P3) is not accessible as program (since UPA = 0).

- The physical data memory is available for accessing as a code segment with offset at A000h.

- Load and Store operations addressed to physical data memory are executed as normal.

- One page (byte access mode) or two pages (word access mode) can be accessed as data with offset at 8000h as determined by the CDA1:0 bits.

When executing from the data memory (only allowable when UPA = 0):

- Program flows freely between the lower 32k user code (P0 and P1) and the utility ROM segment.

- The upper half of the code segment (P2 and P3) is not accessible as program (since UPA = 0).

- The utility ROM can be accessed as data with offset at 8000h.

- One page (byte access mode) or two pages (word access mode) can be accessed as data with offset at 0000h as determined by the CDA1:0 bits.

### 1.2.3.7 Data Alignment

To support merged program and data memory operation while maintaining efficiency on memory space usage, the data memory must be able to support both byte-wide and word-wide accessing. Data is aligned in data memory as word, but the effective data address is resolved to bytes. This data alignment allows direct program fetching in its native word size while maintaining accessibility at the byte level. It is important to realize that this accessibility requires strict word alignment. All executable words must align to an even address in byte mode. Care must be taken when updating the code segment in the unified data memory space as misalignment of words will likely result in loss of program execution control. Worst yet, this situation may not be detected if the watchdog timer is also disabled.

Data memory is organized as two byte-wide memory banks with common word address decode but two 8-bit data buses. The data memory will always be read as a complete word, independent of operation, whether program fetch or data access. The program decoder always uses the full 16-bit word, whereas the data access can utilize a word or an individual byte.

In byte mode, data pointer hardware reads out the word containing the selected byte using the effective data word address pointer (the least significant bit of the byte data pointer is not initially used). Then, the least significant data pointer bit functions as the byte select that is used to place the target byte to the data path. For write access, data pointer hardware addresses a particular word using the effective data word address while the least significant bit selects the corresponding data bank for write, leaving the contents of the other memory bank unaffected.

### 1.2.3.8 Memory Management Unit

Memory allocation and accessing control for program and data memory can be managed by the memory management unit (MMU). A single memory management unit option is discussed in this user's guide, however the memory management unit implementation for any given product depends upon the type and amount of memory addressable by the device. Users should consult the individual product data sheet(s) and/or user's guide supplement(s) for detailed information.

Although supporting less than the maximum addressable program and data memory segments, the MMU implementation presented provides a high degree of programming and access control flexibility. It supports the following:

- User program memory up to 32k x 16 (up to 64k x 16 with inclusion of UPA bit).

- Utility ROM up to 8k x 16.

- Data memory SRAM up to 16k x 16.

- In-system and in-application programming of embedded EEPROM, flash, or SRAM memories.

- Access to any of the three memory areas (SRAM, code memory, utility ROM) using the data memory pointers.

- Execution from any of the three memory areas (SRAM, code memory, factory written and tested utility-ROM routines).

Given these capabilities, the following rules apply to the memory map:

- A particular memory segment cannot be simultaneously accessed as both program and data.

- The offset address is A000h when logically mapping data memory into the program space.

- The offset for logically mapping the utility ROM into the data memory space is 8000h.

- Program memory:

- The lower half of the program memory (P0 and P1) is always accessible, starting at 0000h.

- The upper half of the program memory (P2 and P3) must be activated by setting the UPA bit to 1 when accessing for code execution, starting at 8000h.

- Setting the UPA bit to 1 disallows access to the utility ROM and logical data memory as program.

- Physical program memory pages (P0, P1, P2, P3) are logically mapped into data space based upon the memory segment currently being used for execution, selection of byte/word access mode, and CDA1:0 bit settings (described in the *Pseudo-Von Neumann Memory Access* sections).

- Data memory

- Access can be either word or byte.

- All 16 data pointer address bits are significant in either access mode (word or byte).

Figure 1-5. CDA Functions (Word Access Mode)

Figure 1-6. CDA Functions (Byte Access Mode)

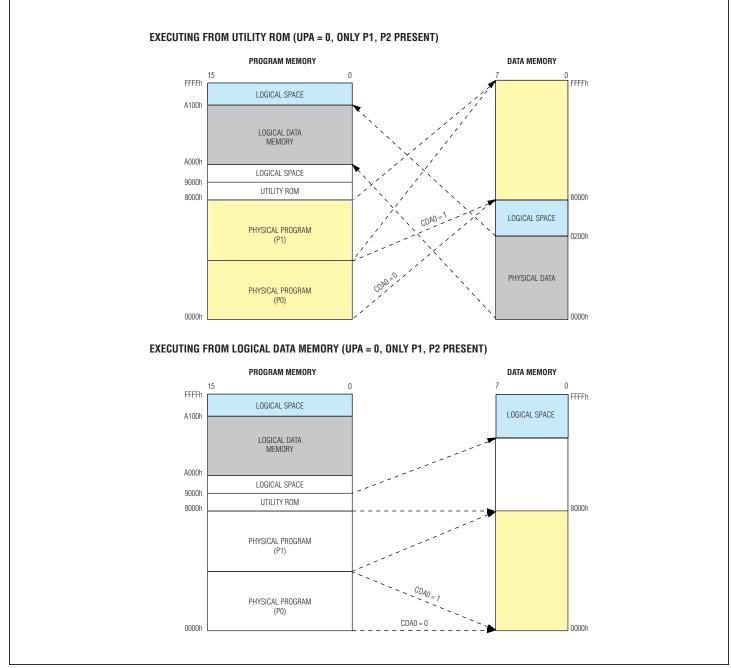

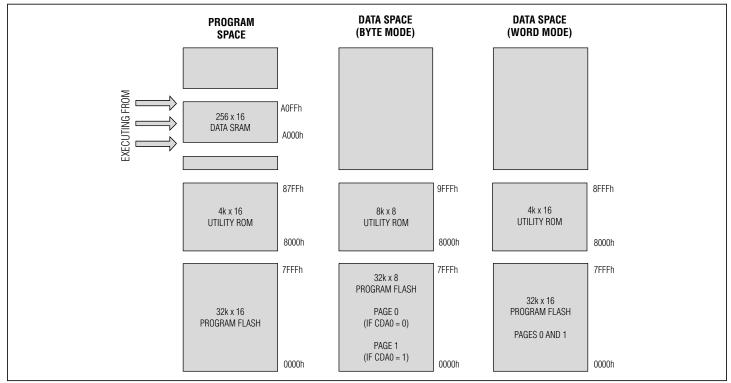

### 1.2.3.9 Program and Data Memory Mapping Example 1: MAXQ7665B

Figures 1-7, 1-8, and 1-9 show the mapping of physical memory segments into the program and data memory space for the MAXQ7665B with  $32k \times 16$  (64kB) program flash memory. In this case and all cases when program flash memory size is  $\leq 32k \times 16$ , the memory mapping is straightforward as there is no overlapping among the program, utility ROM, and data memory segments. The mapping of memory segments into program space is always the same. The mapping of memory segments into data space varies depending on which memory segment is currently being executed from.

In all cases, whichever memory segment is currently being executed from in program space cannot be accessed in data space.

Figure 1-7. MAXQ7665B Memory Map When Executing from Application Flash

Figure 1-8. MAXQ7665B Memory Map When Executing from Utility ROM

Figure 1-9. MAXQ7665B Memory Map When Executing from Data SRAM

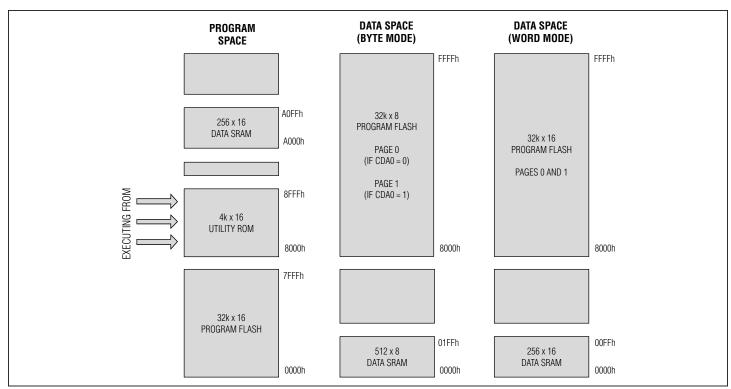

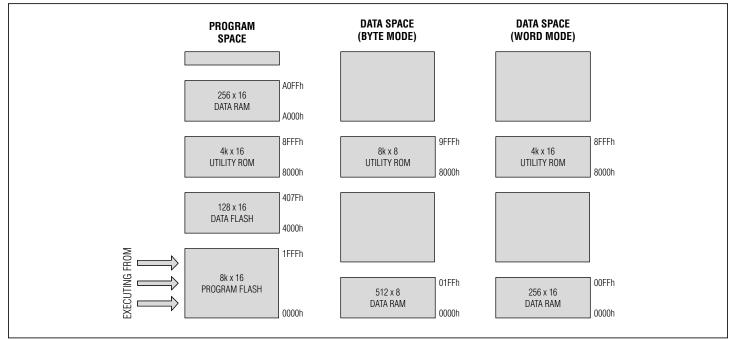

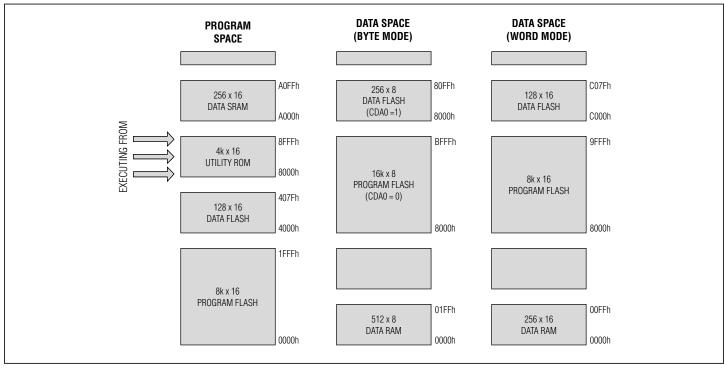

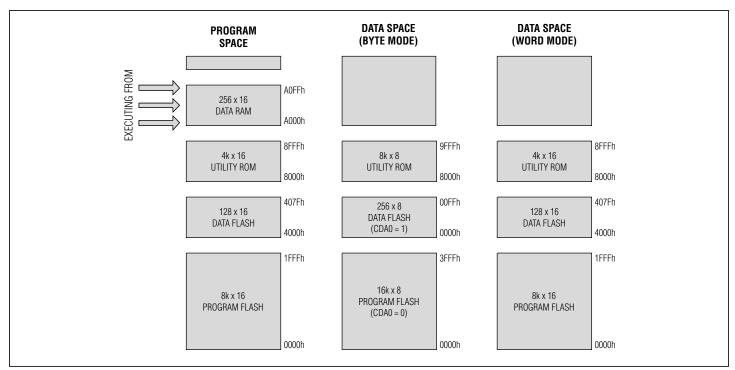

### 1.2.3.10 Program and Data Memory Mapping Example 2: MAXQ7666

Figures 1-10, 1-11, and 1-12 show the mapping of physical memory segments into the program and data memory space for the MAXQ7666 with 8k x 16 (16kB) program flash memory, 256B data flash memory, and 512B data RAM.

Figure 1-10. MAXQ7666 Memory Map When Executing from Application Flash

Figure 1-11. MAXQ7666 Memory Map When Executing from Utility ROM

Figure 1-12. MAXQ7666 Memory Map When Executing from Data RAM

## 1.2.4 Interrupts

The MAXQ7665/MAXQ7666 provide a single, programmable interrupt vector (IV) that can be used to handle internal and external interrupts. Interrupts can be generated from system level sources (e.g., watchdog timer) or by sources associated with the peripheral modules included in the specific MAXQ7665/MAXQ7666 microcontrollers. Only one interrupt can be handled at a time, and all interrupts naturally have the same priority. A programmable interrupt mask register allows software-controlled prioritization and nesting of highpriority interrupts.

### 1.2.4.1 Servicing Interrupts

For the MAXQ7665/MAXQ7666 to service an interrupt, interrupts must be enabled globally, modularly, and locally. The Interrupt Global Enable (IGE) bit located in the Interrupt Control (IC) register acts as a global interrupt mask. This bit defaults to 0, and it must be set to 1 before any interrupt takes place.

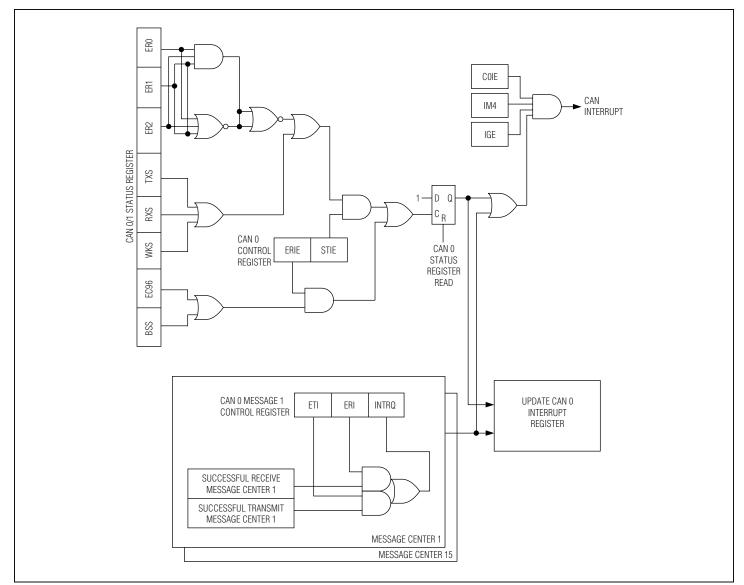

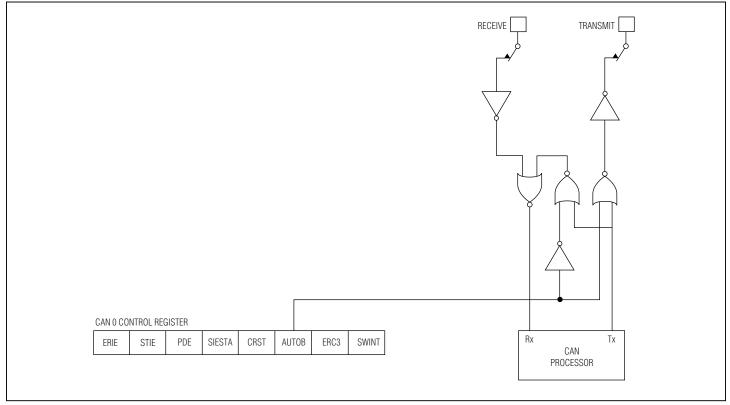

The local interrupt-enable bit for a particular source is in one of the peripheral registers associated with that peripheral module, or in a system register for any system interrupt source. Between the global and local enables are intermediate per-module and system interrupt mask bits. These mask bits reside in the Interrupt Mask system register. By implementing intermediate per-module masking capability in a single register, interrupt sources spanning multiple modules can be selectively enabled/disabled in a single instruction. This promotes a simple, fast, and user-definable interrupt prioritization scheme. The interrupt source-enable hierarchy is illustrated in Figure 1-13.

When an interrupt condition occurs, its individual flag is set, even if the interrupt source is disabled at the local, module, or global level. Interrupt flags must be cleared within the user interrupt routine to avoid repeated interrupts from the same source.

Since all interrupts vector to the address contained in the Interrupt Vector (IV) register, the Interrupt Identification Register (IIR) may be used by the interrupt service routine to determine the module source of an interrupt. The IIR contains a bit flag for each peripheral module and one flag associated with all system interrupts; if the bit for a module is set, then an interrupt is pending that was initiated by that module. If a module is capable of generating interrupts for different reasons, then peripheral register bits inside the module provide a means to differentiate among interrupt sources.

The Interrupt Vector (IV) register provides the location of the interrupt service routine. It may be set to any location within program memory. The IV register defaults to 0000h on reset or power-up, so if it is not changed to a different address, the user program must determine whether a jump to 0000h came from a reset or interrupt source.

### 1.2.4.2 Interrupt System Operation

The interrupt handler hardware responds to any interrupt event when it is enabled. An interrupt event occurs when an interrupt flag is set. All interrupt requests are sampled at the rising edge of the clock and can be serviced by the processor one clock cycle later, assuming the request does not hit the interrupt exception window. The one-cycle stall between detection and acknowledgement/servicing is due to the fact that the current instruction may also be accessing the stack. For this reason, the CPU must allow the current instruction to complete before pushing the stack and vectoring to IV. If an interrupt exception window is generated by the currently executing instruction, the following instruction must be executed, so the interrupt service routine will be delayed an additional cycle.

Interrupt operation in the MAXQ7665/MAXQ7666 CPU is essentially a state machine generated long CALL instruction. When the interrupt handler services an interrupt, it temporarily takes control of the CPU to perform the following sequence of actions:

- 1) The next instruction fetch from program memory is cancelled.

- 2) The return address is pushed on to the stack.

- 3) The INS bit is set to 1 to prevent recursive interrupt calls.

- 4) The instruction pointer is set to the location of the interrupt service routine (contained in the Interrupt Vector register).

- 5) The CPU begins executing the interrupt service routine.

Once the interrupt service routine completes, it should use the RETI instruction to return to the main program. Execution of RETI involves the following sequence of actions:

- 1) The return address is popped off the stack.

- 2) The INS bit is cleared to 0 to re-enable interrupt handling.

- 3) The instruction pointer is set to the return address that was popped off the stack.

- 4) The CPU continues execution of the main program.

Pending interrupt requests will not interrupt an RETI instruction; a new interrupt will be serviced after first being acknowledged in the execution cycle which follows the RETI instruction and then after the standard one stall cycle of interrupt latency. This means there will be at least two cycles between back-to-back interrupts.

### 1.2.4.3 Synchronous vs. Asynchronous Interrupt Sources

Interrupt sources can be classified as either asynchronous or synchronous. All internal interrupts are synchronous interrupts. An internal interrupt is directly routed to the interrupt handler that can be recognized in one cycle. All external interrupts are asynchronous interrupts by nature. When the device is not in stop mode, asynchronous interrupt sources are passed through a 3-clock sampling/glitch filter circuit before being routed to the interrupt handler. The sampling/glitch filter circuit is running on the undivided source clock (i.e., before PMME, CD1:0-controlled clock divide) such that the number of system clocks required to recognize an asynchronous interrupt request depends upon the system clock divide ratio:

- if the system clock divide ratio is 1, the interrupt request is recognized after 3 system clock;

- if the system clock divide ratio is 2, the interrupt request is recognized after 2 system clock;

- if the system clock divide ratio is 4 or greater, the interrupt request is recognized after 1 system clock;

An interrupt request with a pulse width less than three undivided clock cycles is not recognized. Note that the granularity of interrupt source is at module level. Synchronous interrupts and sampled asynchronous interrupts assigned to the same module produce a single interrupt to the interrupt handler.

External interrupts, when enabled, can be used as switchback sources from power management mode. There is no latency associated with the switchback because the circuit is being clocked by an undivided clock source versus the divide-by-256 system clock. For the same reason, there is no latency for other switchback sources that do not qualify as interrupt sources.

### 1.2.4.4 Interrupt Prioritization by Software

All interrupt sources of the MAXQ7665/MAXQ7666 microcontrollers naturally have the same priority. However, when CPU operation vectors to the programmed Interrupt Vector address, the order in which potential interrupt sources are interrogated is left entirely up to the user, as this often depends upon the system design and application requirements. The Interrupt Mask system register provides the ability to knowingly block interrupts from modules considered to be of lesser priority and manually re-enable the interrupt servicing by the CPU (by setting INS = 0). Using this procedure, a given interrupt service routine can continue executing, only to be interrupted by higher priority interrupts. An example demonstrating this software prioritization is provided in *Section 1.3.8: Handling Interrupts*.

### 1.2.4.5 Interrupt Exception Window

An interrupt exception window is a noninterruptable execution cycle. During this cycle, the interrupt handler does not respond to any interrupt requests. All interrupts that would normally be serviced during an interrupt exception window are delayed until the next execution cycle.

Interrupt exception windows are used when two or more instructions must be executed consecutively without any delays in between. Currently, there is a single condition in the MAXQ7665/MAXQ7666 microcontrollers that causes an interrupt exception window: activation of the prefix (PFX) register.

When the prefix register is activated by writing a value to it, it retains that value only for the next clock cycle. For the prefix value to be used properly by the next instruction, the instruction that sets the prefix value and the instruction that uses it must always be executed back to back. Therefore, writing to the PFX register causes an interrupt exception window on the next cycle. If an interrupt occurs during an interrupt exception window, an additional latency of one cycle in the interrupt handling will be caused as the interrupt will not be serviced until the next cycle.

### 1.2.4.6 MAXQ7665/MAXQ7666 Interrupt Sources

Table 1-6 lists all possible interrupt sources for the MAXQ7665/MAXQ7666, along with their corresponding module interrupt enable bits, local interrupt enable bits, and interrupt flags.

- Each module interrupt enable bit, when cleared to 0, will block interrupts originating in that module from being acknowledged. When the module interrupt enable bit is set to 1, interrupts from that module are acknowledged (unless the interrupts have been disabled globally).

- Each local interrupt enable bit, when cleared to 0, will disable the corresponding interrupt. When the local interrupt enable bit is set to 1, the interrupt will be triggered whenever the interrupt flag is set to 1 (either by software or hardware).

- All interrupt flag bits cause the corresponding interrupt to trigger when the bit is set to 1. These bits are typically set by hardware and must be cleared by software (generally in the interrupt handler routine).

Note that for an interrupt to fire, the following five conditions must exist:

- 1) Interrupts must be enabled globally by setting IGE (IC.0) to 1.

- 2) The module interrupt enable bit for that interrupt source's module must be set to 1.

- 3) The local interrupt enable bit for that specific interrupt source must be set to 1.

- 4) The interrupt flag for that interrupt source must be set to 1. Typically, this is done by hardware when the condition that requires interrupt service occurs.

- 5) The Interrupt In Service (INS) bit must be cleared to 0. This bit is set automatically upon vectoring to the interrupt handler address and cleared automatically upon exit (RETI/POPI), so the only reason to clear this bit manually (inside the interrupt handler routine) is allow nested interrupt handling.

# Table 1-6. MAXQ7665/MAXQ7666 Interrupt Sources and Control Bits

| INTERRUPT                        | MODULE ENABLE BIT        | LOCAL ENABLE BIT | INTERRUPT FLAG  |  |

|----------------------------------|--------------------------|------------------|-----------------|--|

| Watchdog Interrupt IMS (IMR.7)   |                          | EWDI (WDCN.6)    | WDIF (WDCN.3)   |  |

| External Interrupt 0 IM0 (IMR.0) |                          | EX0 (EIE0.0)     | IE0 (EIF0.0)    |  |

| External Interrupt 1             | IM0 (IMR.0)              | EX1 (EIE0.1)     | IE1 (EIF0.1)    |  |

| External Interrupt 2             | IM0 (IMR.0)              | EX2 (EIE0.2)     | IE2 (EIF0.2)    |  |

| External Interrupt 3             | IM0 (IMR.0)              | EX3 (EIE0.3)     | IE3 (EIF0.3)    |  |

| External Interrupt 4             | IM0 (IMR.0)              | EX4 (EIE0.4)     | IE4 (EIF0.4)    |  |

| External Interrupt 5             | IM0 (IMR.0)              | EX5 (EIE0.5)     | IE5 (EIF0.5)    |  |

| External Interrupt 6             | IM0 (IMR.0)              | EX6 (EIE0.6)     | IE6 (EIF0.6)    |  |

| External Interrupt 7             | IM0 (IMR.0)              | EX7 (EIE0.7)     | IE7 (EIF0.7)    |  |

| Serial Port Receive              | IM0 (IMR.0)              | ESI (SMD0.2)     | RI (SCON0.0)    |  |

| Serial Port Transmit             | IM0 (IMR.0)              | ESI (SMD0.2)     | TI (SCON0.1)    |  |

| SPI Mode Fault                   | IM1 (IMR.1)              | ESPII (SPICF.7)  | MODF (SPICN.3)  |  |

| SPI Write Collision              | IM1 (IMR.1)              | ESPII (SPICF.7)  | WCOL (SPICN.4)  |  |

| SPI Receive Overrun              | IM1 (IMR.1)              | ESPII (SPICF.7)  | ROVR (SPICN.5)  |  |

| SPI Transfer Complete            | IM1 (IMR.1)              | ESPII (SPICF.7)  | SPIC (SPICN.6)  |  |

| Timer 0—Low Compare              | IM2 (IMR.2)              | ET2L (T2CNB0.7)  | T2CL (T2CNB0.0) |  |

| Timer 0—Low Overflow             | IM2 (IMR.2)              | ET2L (T2CNB0.7)  | TF2L (T2CNB0.2) |  |

| Timer 0—Capture/Compare          | IM2 (IMR.2)              | ET2 (T2CNA0.7)   | TCC2 (T2CNB0.1) |  |

| Timer 0—Overflow                 | IM2 (IMR.2)              | ET2 (T2CNA0.7)   | TF2 (T2CNB0.3)  |  |

| Timer 1—Low Compare              | –Low Compare IM2 (IMR.2) |                  | T2CL (T2CNB1.0) |  |

| Timer 1—Low Overflow IM2 (IMR.2) |                          | ET2L (T2CNB1.7)  | TF2L (T2CNB1.2) |  |

| Timer 1—Capture/Compare          | IM2 (IMR.2)              | ET2 (T2CNA1.7)   | TCC2 (T2CNB1.1) |  |

| Timer 1—Overflow                 | IM2 (IMR.2)              | ET2 (T2CNA1.7)   | TF2 (T2CNB1.3)  |  |

| Timer 2—Low Compare              | IM3 (IMR.3)              | ET2L (T2CNB2.7)  | T2CL (T2CNB2.0) |  |

| Timer 2—Low Overflow             | IM3 (IMR.3)              | ET2L (T2CNB2.7)  | TF2L (T2CNB2.2) |  |

| Timer 2—Capture/Compare          | IM3 (IMR.3)              | ET2 (T2CNA2.7)   | TCC2 (T2CNB2.1) |  |

| Timer 2—Overflow                 | IM3 (IMR.3)              | ET2 (T2CNA2.7)   | TF2 (T2CNB2.3)  |  |

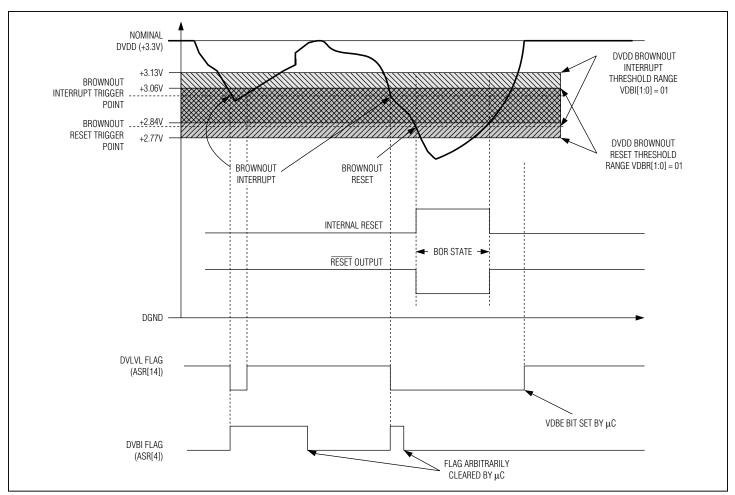

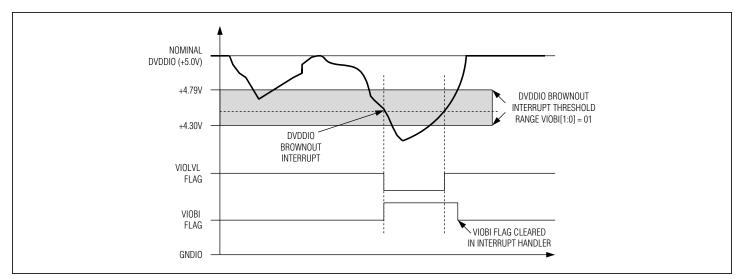

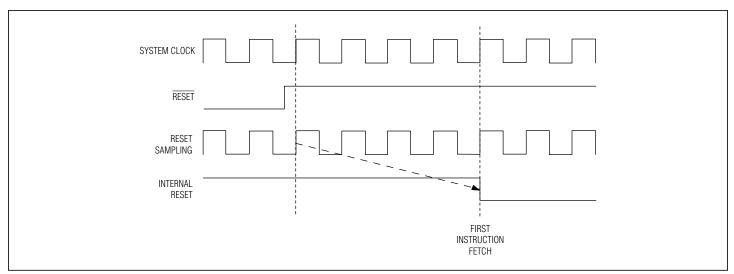

| CAN 0 Message Center 1 Receive   | IM4 (IMR.4)              | ERI (COM1C.5)    | INTRQ (C0M1C.4) |  |